SPRADG4A January 2024 – April 2024

- 1

- Abstract

- Trademarks

- 1General Texas Instruments High Voltage Evaluation (TI HV EVM) User Safety Guidelines

- 2Introduction

- 3System Description

- 4System Overview

- 5Hardware

-

6Software

- 6.1 Getting Started With Firmware

- 6.2 SysConfig Setup

- 6.3 Incremental Builds

- 7Testing and Results

- 8References

- 9Revision History

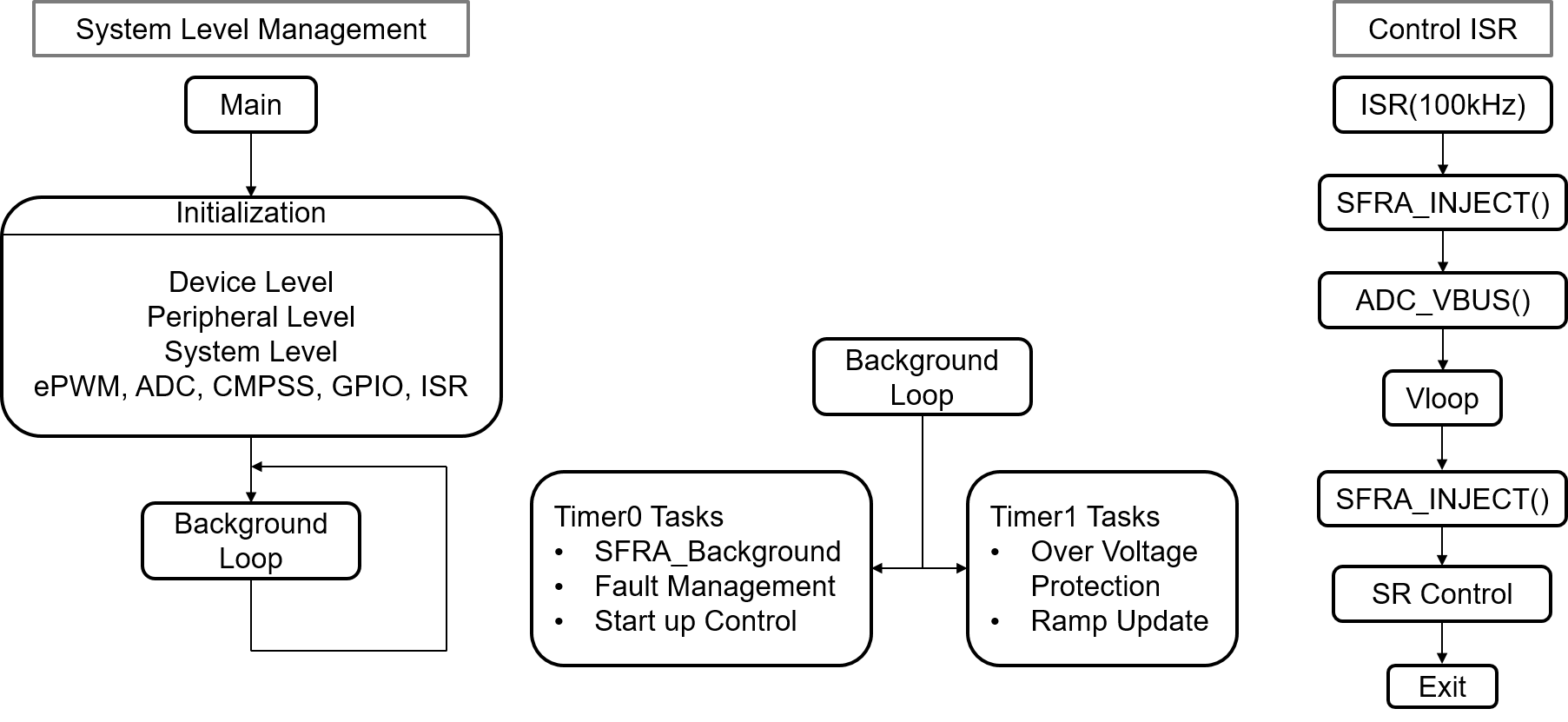

6.1.2 Software Architecture

The project flow contains initialization of all the peripheral clocks and submodules of the system on a chip (SOC) using the AM263x SysConfig Tool and MCU_PLUS_SDK_AM263x. Initializing the Peripheral IPs used in this design like EPWM, ADC, CMPSS and so forth, are discussed in Section 6.2.

The Software contains one ISRs and one background task. The code flow is described in Figure 6-2. The ISR is scheduled to run every 10μs. It contains the main control loop explained in Section 4.3.1.

Figure 6-2 Software Block Diagram

Figure 6-2 Software Block Diagram