SPRADH9 June 2024 AM6442

- 1

- Abstract

- Trademarks

- 1Abbreviations

- 2Introduction

- 3X86 as RC and AM64x as EP

- 4Test Setup

-

5PCIe Test Specification

- 5.1 Identification and Configuration Functionalities

- 5.2 Reference Clock Functionalities

- 5.3 Inbound ATU and BAR Functionalities

- 5.4 Outbound ATU Functionalities

- 5.5 MSI Functionality

- 5.6 Downstream Interrupt Functionality

- 5.7 Device Power Management State Functionality

- 5.8 Function Level Reset Mechanism

- 5.9 Legacy Interrupt Mechanism

- 5.10 MSI-X Capability

- 5.11 Hot Reset Mechanism

- 6Windows Example Driver Verification

- 7References

2.1.4 PCIe Aggregate Throughput

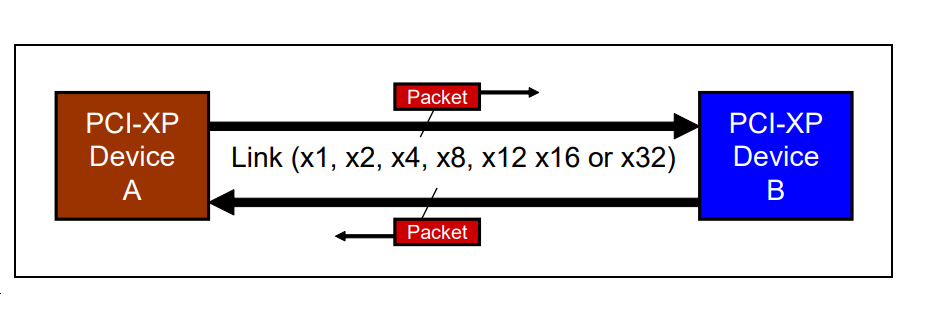

A PCI Express interconnect is referred to as a Link, and connects two devices. A link consists of either 1, 2, 4, 8, 12, 16 or 32 signals in each direction (note, because the system uses full-differential signaling, each signal actually needs two wires). These signals are referred to as Lanes. A designer determines how many lanes to implement based on the targeted performance benchmark required on a given link. In the nomenclature, the width of a link is shown with an x in front of a number, where the x is pronounced as by, so that a link with 4 signals in each direction, for example, is referred to as by four link.

Figure 2-3 PCIE Express Link

Figure 2-3 PCIE Express LinkTable 2-1 shows the aggregate bandwidth numbers for various Link width implementations. As is apparent from this table, the peak bandwidth achievable with PCI Express is significantly higher than most existing buses today.

Consider how these bandwidth numbers are calculated. The transmission/reception rate is currently 2.5 Gbits/sec per Lane per direction. To support a greater degree of robustness during data transmission and reception, each byte of data to be transmitted is converted into a 10-bit code (via an 8b/10b encoder in the transmitter device). In other words, for every Byte of data to be sent, 10-bits of encoded data are actually transmitted. The result is a 25% overhead to transmit a byte of data. PCI Express implements a dual-simplex Link which implies that data is both transmitted and received simultaneously.

The aggregate bandwidth assumes simultaneous traffic in both directions. To obtain the aggregate bandwidth numbers in Table 2-1, multiply 2.5 Gbits per second by 2 (to account for both directions), then multiply by the number of Lanes, and finally divide by 10-bits per Byte (to account for the 8-to-10 bit encoding) to arrive at a bytes per second result.

| PCIExpress Link Width | x1 | x2 | x4 | x8 | x12 | x16 | x32 |

|---|---|---|---|---|---|---|---|

| AggregateBand- width (GBytes/sec) | 0.5 | 1 | 2 | 4 | 6 | 8 | 16 |