SPRADH9 June 2024 AM6442

- 1

- Abstract

- Trademarks

- 1Abbreviations

- 2Introduction

- 3X86 as RC and AM64x as EP

- 4Test Setup

-

5PCIe Test Specification

- 5.1 Identification and Configuration Functionalities

- 5.2 Reference Clock Functionalities

- 5.3 Inbound ATU and BAR Functionalities

- 5.4 Outbound ATU Functionalities

- 5.5 MSI Functionality

- 5.6 Downstream Interrupt Functionality

- 5.7 Device Power Management State Functionality

- 5.8 Function Level Reset Mechanism

- 5.9 Legacy Interrupt Mechanism

- 5.10 MSI-X Capability

- 5.11 Hot Reset Mechanism

- 6Windows Example Driver Verification

- 7References

5.5 MSI Functionality

Test

Description:

Test to verify if MSI IRQs are sent correctly from the PCIe EP to the address configured by the RC.

Execution:

- Run PCIe EP application pcie_enumerate_ep.

- Run Linux-based RC test application ti-sample-vfio.

- Check status of both programs. As ti-sample-vfio waits for MSI IRQs sent by PCIe EP on specified address, it can terminate without any failure ensuring correct functionality of PCIe EP MSI mechanism.

Test

Description:

Test to verify if the maximum number of different MSI IRQs (multi-message capable) available in the PCIe EP is determined correctly in the PCIe RC and if a reduced number of desired MSI IRQs (multi-message enable) can be requested from the RC.

Execution:

- Run PCIe EP application pcie_enumerate_ep with the default number of MSI IRQs set as 16.

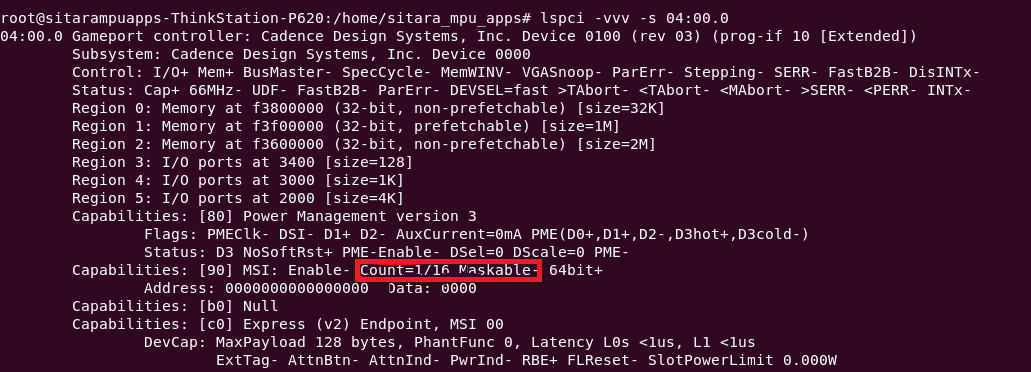

- On Linux-based RC hardware check PCIe EP MSI capability on offset 90. The MSI capability can be disabled with a count set to 1 out of 16 as shown in the following figure.

- Run Linux-based RC test application

ti-sample-vfio. Pass the default number of configured MSI IRQs as the

desired number of MSI IRQs being tested as the fifth

parameter:

sudo ./ti-sample-vfio 9 0 0 19 16 - Continue ti-sample-vfio with enter until the program halts at status output Initialize MSI test. Expect 16 distinct MSI IRQs.

- Open a second Linux terminal and check the PCIe EP MSI capability at offset 90. The MSI mechanism can be enabled with a count of 16 as shown in the following figure.

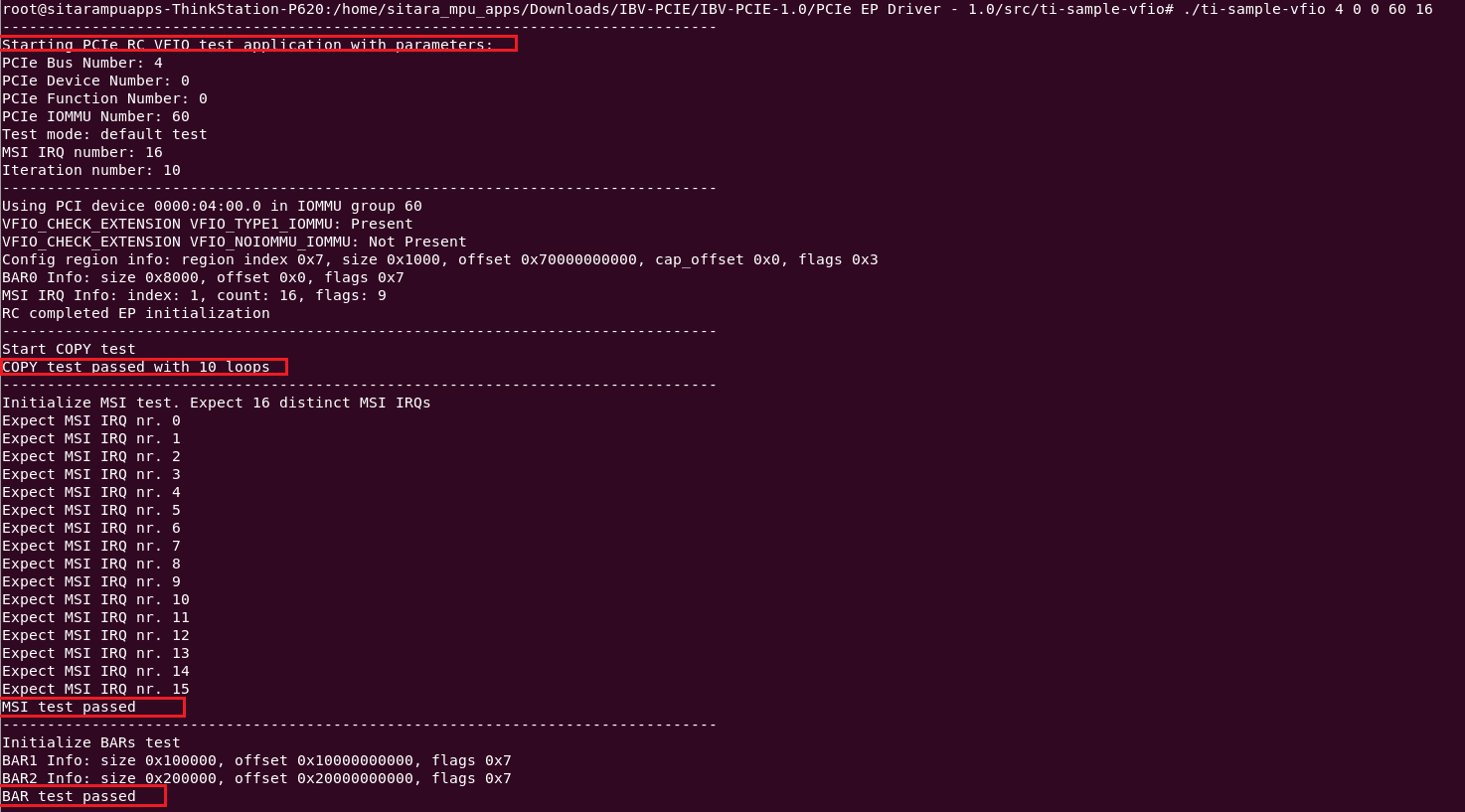

- Continue ti-sample-vfio. The program can continue normally, perform an extended MSI test with 16 MSI IRQs and end without any failure as shown in the following figure.

- Run Linux-based RC test application

ti-sample-vfio. Configure the number of MSI IRQs to be tested with

less than the default number, for example,

8:

sudo ./ti-sample-vfio 9 0 0 19 8 - Continue ti-sample-vfio with enter until

the program halts at status output

- Initialize MSI test. Expect 8 distinct MSI IRQs.

- Check the PCIe EP MSI capability at offset 90 on second Linux terminal. The MSI capability can be enabled with the count 8 out of 16 as shown in the following figure.

- Continue ti-sample-vfio. The program can continue normally, perform an extended MSI test with 8 MSI IRQs and end without any failure as shown in the following figure.

- On Linux-based RC hardware check PCIe EP MSI

capability on offset 90. The MSI capability can be disabled with a count set to

1 out of 16 as shown in the following figure.

Test

Description:

Test to verify is MSI per vector masking is disabled correctly at TMDS243EVM/TMDS64EVM PCIe EP.

Execution:

- On Linux-based RC hardware, check PCIe EP MIS

capability with Linux terminal. The maskable filed can be disabled as shown in

the following figure.