SPRADJ9 August 2024 AM62P

2.3 AM62P Display Subsystem Clocking Architecture

The AM62Px family of SoCs have two instances of the DSS controller (DSS0 and DSS1). These two DSS controllers are backed by three PLLs giving a possibility of a maximum of three independent streams of video data, namely OLDI, DPI, and DSI.

The two OLDIs can then be configured in the clone mode to have one pair of two cloned displays + two more independent displays giving a total output for four video sinks. There are two OLDI TXs available at the disposal (DSS0) of VP0 and a DPI output from VP1. DSS1 VP0 can only output to one of the two available OLDI TXs, allowing for a single-link mode. However, DSS1 VP0 can also bypass the OLDI TXs and simply provide a DPI output on the SoC.

DSS1 VP1 can also provide a DPI output. Along with that, the DSS1 VP1 can instead redirect the output to the DSI controllers and help send out DSI signals out of the SoC.

There are three VPs (DSS0-VP1, DSS1-VP0, DSS1-VP1) capable of driving DPI signals out of the SoC, but only one can do that at a given time. The DPI outputs of all these VPs are passed through a MUX and only a single set of DPI signals come out of the SoC.

PLL16 is the dedicated OLDI PLL and is only being used with DSS0-VP0. This PLL helps provide a maximum of 2.1GHz for dual-link mode operations.

PLL17 is the DPI PLL and provides pixel clock to all the three DPI output capable VPs, DSS0-VP1, DSS1-VP0, and DSS1-VP1. The maximum frequency is 165MHz. In a single case, PLL17 provides a 300MHz pixel frequency to DSS1-VP1 to drive a DSI output. This happens when the DSI PLL (PLL18) is being used to drive a single link output from DSS1-VP0.

PLL18 doubles as a DSI or OLDI clock. For DSI purposes, PLL18 provides a clock with a maximum frequency of 300MHz to DSS1-VP1. For the OLDI purposes, PLL18 supports the DSS1-VP0 for a single link OLDI output.

Figure 2-3 PLL18 Provides Clock Input for OLDIs TX in Dual-Link Mode or Single-Link Mode

PLL16 provides clock input for OLDI

TXs in dual-link mode or single-link mode operation. Enabling

oldi_enable_cfg0 in DSS0 VP0 divides the input PLL16 clock by

seven times as input to DSS0 VP0 pixel clock. Enabling dual_cfg0 in

DSS0 VP0 divides the input PLL16 clock by two times for the PLL clock of OLDI TXs.

PLL18 provides clock input for OLDI TX1 in single link mode. Enabling oldi_enable_cfg0 in DSS1 VP0 divides the input PLL8 clock by 7 times as input to DSS1 VP0 pixel clock.

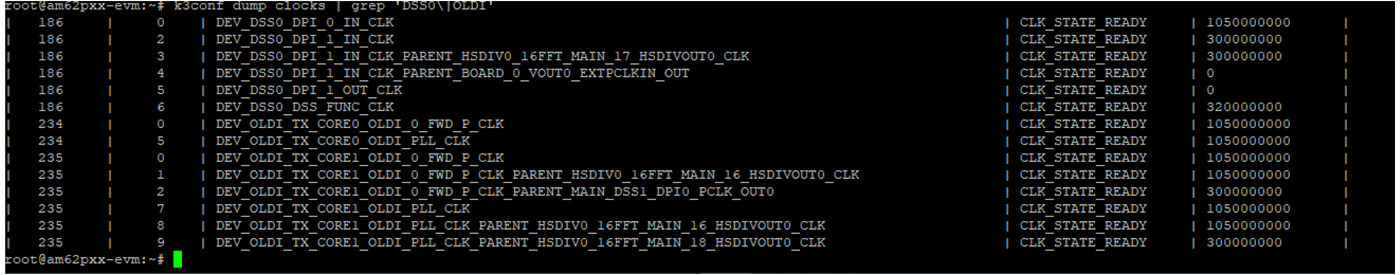

Figure 2-4 shows the screenshot of the DSS0 clock using the k3conf tool, also known as a K3conf clock dump snippet.

Figure 2-4 DSS0 Clock Using K3 Configuration Tool

The following sections of the application note provide the requirements and steps to integrate the LVDS panel on Linux and the RTOS.