SPRADJ9 August 2024 AM62P

5 Steps for Integration (RTOS)

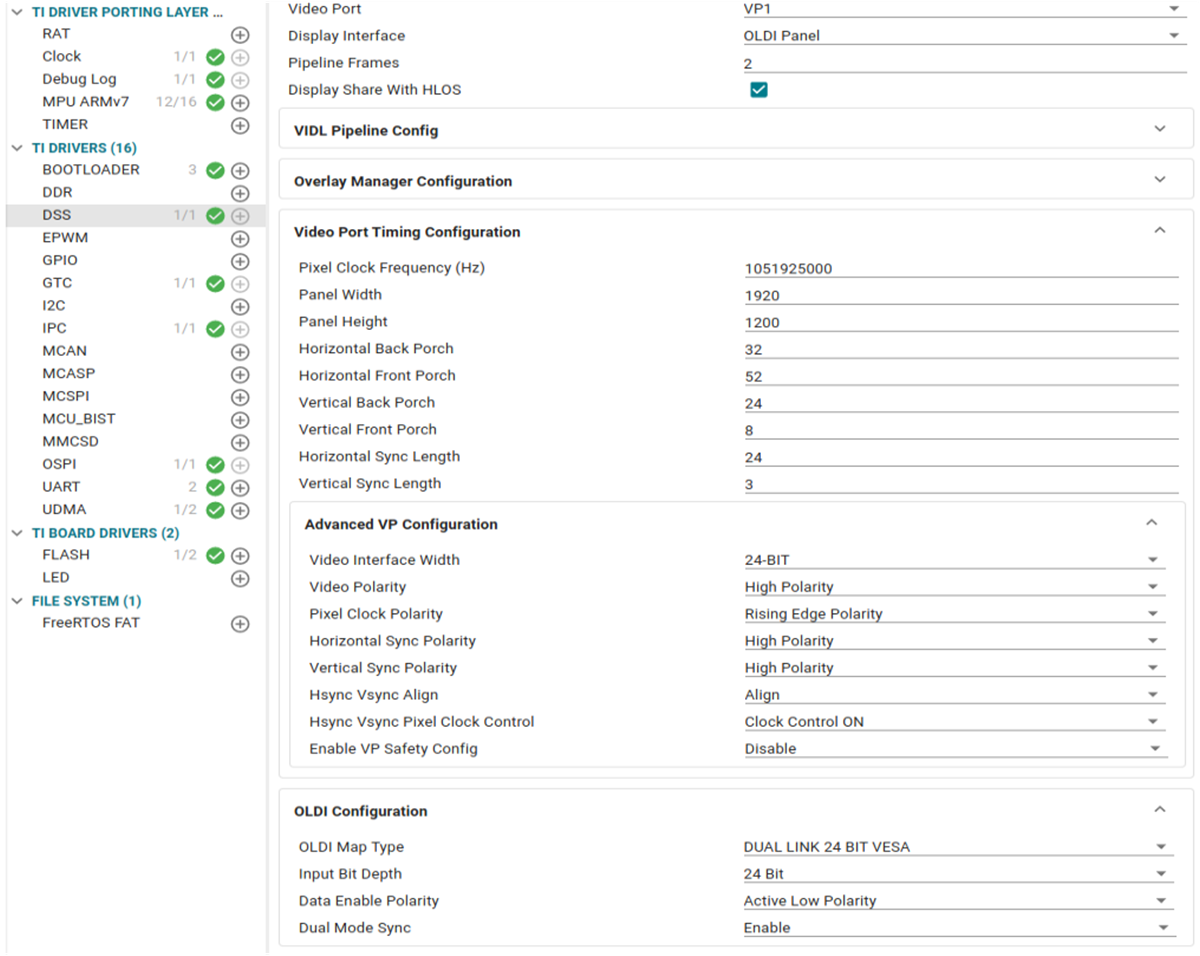

Integrate a new LVDS panel in RTOS using this SysConfig configurator which is part of the MCU_PLUS_SDK. The sysconfig for the DSS driver provides the following configuration tabs to integrate a new LVDS panel.

- Video Port Timing Configuration:

- Configure the Pixel Clock Frequency required for the panel

- Timing parameters HSYNC, VSYNC, VFP, VBP, HFP, HBP and more

- Interface width: 24 bit or 18 bit

- Timing signals polarity

- OLDI Configuration:

- Map type for OLDI: VESA, JEIDA, 24-bit or 18-bit standards

- Input bit width: Whether panel connected expects 24-bit or 18-bit input

- Dual link mode: Enable or disable dual-link mode

- Data enable signal polarity

Figure 5-1 SysConfig Configurator