SPRUIT5 April 2021 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1

- Trademarks

- 1Introduction

- 2TMS320F28002x Product Safety Capability and Constraints

- 3TI Development Process for Management of Systematic Faults

- 4TMS320F28002x Product Overview

-

5Brief Description of Safety Elements

- 5.1 TMS320F28002x MCU Infrastructure Components

- 5.2 Processing Elements

- 5.3 Memory (Flash, SRAM and ROM)

- 5.4 On-Chip Communication Including Bus-Arbitration

- 5.5 Digital I/O

- 5.6 Analog I/O

- 5.7

Data Transmission

- 5.7.1 Controller Area Network (DCAN)

- 5.7.2 Serial Peripheral Interface (SPI)

- 5.7.3 Serial Communication Interface (SCI)

- 5.7.4 Inter-Integrated Circuit (I2C)

- 5.7.5 Fast Serial Interface (FSI)

- 5.7.6 Local Interconnect Network (LIN)

- 5.7.7 Power Management Bus Module (PMBus)

- 5.7.8 Host Interface Controller (HIC)

-

6Brief Description of Diagnostics

- 6.1

TMS320F28002x MCU Infrastructure Components

- 6.1.1 Clock Integrity Check Using CPU Timer

- 6.1.2 Clock Integrity Check Using HRPWM

- 6.1.3 Clock Integrity Check Using DCC

- 6.1.4 EALLOW Protection for Critical Registers

- 6.1.5 Efuse Autoload Self-Test

- 6.1.6 Efuse ECC

- 6.1.7 Efuse ECC Logic Self-Test

- 6.1.8 External Monitoring of Clock via XCLKOUT

- 6.1.9 External Monitoring of Warm Reset (XRSn)

- 6.1.10 External Voltage Supervisor

- 6.1.11 External Watchdog

- 6.1.12 Glitch Filtering on Reset Pins

- 6.1.13 Hardware Disable of JTAG Port

- 6.1.14 Internal Watchdog (WD)

- 6.1.15 Lock Mechanism for Control Registers

- 6.1.16 Missing Clock Detect (MCD)

- 6.1.17 NMIWD Reset Functionality

- 6.1.18 NMIWD Shadow Registers

- 6.1.19 Multi-Bit Enable Keys for Control Registers

- 6.1.20 Online Monitoring of Temperature

- 6.1.21 Periodic Software Read Back of Static Configuration Registers

- 6.1.22 Peripheral Clock Gating (PCLKCR)

- 6.1.23 Peripheral Soft Reset (SOFTPRES)

- 6.1.24 PLL Lock Profiling Using On-Chip Timer

- 6.1.25 PLL lock indication

- 6.1.26 Reset Cause Information

- 6.1.27 Software Read Back of Written Configuration

- 6.1.28 Software Test of ERRORSTS Functionality

- 6.1.29 Software Test of Missing Clock Detect Functionality

- 6.1.30 Software test of DCC functionality including error tests

- 6.1.31 Interleaving of FSM states

- 6.1.32 Software Test of Reset

- 6.1.33 Software Test of Watchdog (WD) Operation

- 6.1.34 Brownout Reset (BOR)

- 6.1.35 Dual clock comparator (DCC) - Type 2

- 6.2

Processing Elements

- 6.2.1 CPU Hardware Built-In Self-Test (HWBIST)

- 6.2.2 CPU Hardware Built-In Self-Test (HWBIST) Auto-Coverage

- 6.2.3 CPU Hardware Built-In Self-Test (HWBIST) Timeout Feature

- 6.2.4 CPU Hardware Built-In Self-Test (HWBIST) Fault Injection Capability

- 6.2.5 CPU Handling of Illegal Operation, Illegal Results and Instruction Trapping

- 6.2.6 Stack Overflow Detection

- 6.2.7 VCRC Check of Static Memory Contents

- 6.2.8 VCRC Auto Coverage

- 6.2.9 Embedded Real Time Analysis and Diagnostic (ERAD)

- 6.2.10 Inbuilt hardware redundancy in ERAD bus comparator module

- 6.3

Memory (Flash, SRAM and ROM)

- 6.3.1 Bit Multiplexing in Flash Memory Array

- 6.3.2 Bit Multiplexing in SRAM Memory Array

- 6.3.3 Data Scrubbing to Detect/Correct Memory Errors

- 6.3.4 Flash ECC

- 6.3.5 Flash Program Verify and Erase Verify Check

- 6.3.6 Software Test of ECC Logic

- 6.3.7 Software Test of Flash Prefetch, Data Cache and Wait-States

- 6.3.8 Access Protection Mechanism for Memories

- 6.3.9 SRAM ECC

- 6.3.10 SRAM Parity

- 6.3.11 Software Test of Parity Logic

- 6.3.12 Software Test of SRAM

- 6.3.13 Memory Power-On Self-Test (MPOST)

- 6.3.14 Background CRC

- 6.3.15 Watchdog for Background CRC

- 6.4

On-Chip Communication Including Bus-Arbitration

- 6.4.1 1oo2 Software Voting Using Secondary Free Running Counter

- 6.4.2 DMA Overflow Interrupt

- 6.4.3 Maintaining Interrupt Handler for Unused Interrupts

- 6.4.4 Power-Up Pre-Operational Security Checks

- 6.4.5 Majority Voting and Error Detection of Link Pointer

- 6.4.6 PIE Double SRAM Hardware Comparison

- 6.4.7 PIE Double SRAM Comparison Check

- 6.4.8 Software Check of X-BAR Flag

- 6.4.9 Software Test of ePIE Operation Including Error Tests

- 6.4.10 Disabling of Unused DMA Trigger Sources

- 6.4.11 Software Test of CLB Function Including Error Tests

- 6.4.12 Monitoring of CLB by eCAP or eQEP

- 6.4.13 Periodic Software Read Back of SPI Buffer

- 6.4.14 Timeout detection through ERAD counter

- 6.5

Digital I/O

- 6.5.1 eCAP Application Level Safety Mechanism

- 6.5.2 ePWM Application Level Safety Mechanism

- 6.5.3 ePWM Fault Detection Using X-BAR

- 6.5.4 ePWM Synchronization Check

- 6.5.5 eQEP Application Level Safety Mechanism

- 6.5.6 eQEP Quadrature Watchdog

- 6.5.7 eQEP Software Test of Quadrature Watchdog Functionality

- 6.5.8 Hardware Redundancy

- 6.5.9 HRPWM Built-In Self-Check and Diagnostic Capabilities

- 6.5.10 Information Redundancy Techniques

- 6.5.11 Monitoring of ePWM by eCAP

- 6.5.12 Monitoring of ePWM by ADC

- 6.5.13 Online Monitoring of Periodic Interrupts and Events

- 6.5.14 SD Modulator Clock Fail Detection Mechanism

- 6.5.15 Software Test of Function Including Error Tests

- 6.5.16 Monitoring of HRPWM by HRCAP

- 6.5.17 HRCAP Calibration Logic Test Feature

- 6.5.18 QMA Error Detection Logic

- 6.6

Analog I/O

- 6.6.1 ADC Information Redundancy Techniques

- 6.6.2 ADC Input Signal Integrity Check

- 6.6.3 ADC Signal Quality Check by Varying Acquisition Window

- 6.6.4 CMPSS Ramp Generator Functionality Check

- 6.6.5 DAC to ADC Loopback Check

- 6.6.6 Opens/Shorts Detection Circuit for ADC

- 6.6.7 VDAC Conversion by ADC

- 6.6.8 Disabling Unused Sources of SOC Inputs to ADC

- 6.7

Data Transmission

- 6.7.1 Information Redundancy Techniques Including End-to-End Safing

- 6.7.2 Bit Error Detection

- 6.7.3 CRC in Message

- 6.7.4 DCAN Acknowledge Error Detection

- 6.7.5 DCAN Form Error Detection

- 6.7.6 DCAN Stuff Error Detection

- 6.7.7 I2C Access Latency Profiling Using On-Chip Timer

- 6.7.8 I2C Data Acknowledge Check

- 6.7.9 Parity in Message

- 6.7.10 SCI Break Error Detection

- 6.7.11 Frame Error Detection

- 6.7.12 Overrun Error Detection

- 6.7.13 Software Test of Function Using I/O Loopback

- 6.7.14 SPI Data Overrun Detection

- 6.7.15 Transmission Redundancy

- 6.7.16 FSI Data Overrun/Underrun Detection

- 6.7.17 FSI Frame Overrun Detection

- 6.7.18 FSI CRC Framing Checks

- 6.7.19 FSI ECC Framing Checks

- 6.7.20 FSI Frame Watchdog

- 6.7.21 FSI RX Ping Watchdog

- 6.7.22 FSI Tag Monitor

- 6.7.23 FSI Frame Type Error Detection

- 6.7.24 FSI End of Frame Error Detection

- 6.7.25 FSI Register Protection Mechanisms

- 6.7.26 LIN Physical Bus Error Detection

- 6.7.27 LIN No-Response Error Detection

- 6.7.28 LIN Checksum Error Detection

- 6.7.29 Data Parity Error Detection

- 6.7.30 LIN ID Parity Error Detection

- 6.7.31 PMBus Protocol CRC in Message

- 6.7.32 Clock Timeout

- 6.7.33 Communication Access Latency Profiling Using On-Chip Timer

- 6.7.34 Signature mechanism for interrupt and acknowlegdement in software

- 6.7.35 Software Timeout mechansim for interrupt logic

- 6.7.36 Access protection enable for read/write operations in software

- 6.7.37 Detection of illegal access sequences or access types from host to device

- 6.7.38 Detection of simultaneous MMR access by host and device

- 6.7.39 Enabling locking mechanism for registers

- 6.7.40 Disabling of unused EVENTRIG trigger sources

- 6.1

TMS320F28002x MCU Infrastructure Components

- 7References

- A Safety Architecture Configurations

- B Distributed Developments

- C Summary of Safety Features and Diagnostics

- D Glossary

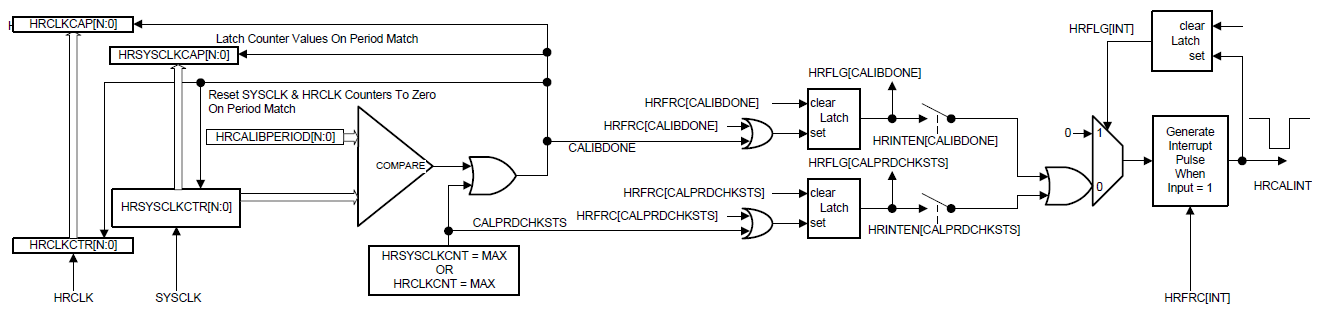

6.5.17 HRCAP Calibration Logic Test Feature

The calibration logic consists of two free-running counters; one clocked by HRCLK(HRCLKCTR) and the other clocked by SYSCLK(HRSYSCLKCTR). When HRSYSCLKCTR is equal to HRCALIBPERIOD, the calibration block will capture and reset both counter values, then trigger an interrupt indicating a new scale factor is ready to be calculated. The scale factor can be found by dividing HRSYSCLKCAP by HRCLKCAP, see Equation 1. This scale factor computation should be done inside of the calibration interrupt service routine. After computing scale factor, Equation 2 can be applied to get actual measurement of captured value from raw count.

The full details of the calibration block are described in Figure 6-4.

Figure 6-4 HRCAP Calibration

Figure 6-4 HRCAP Calibration

Even with calibration, noise on the 1.2 V VDD supply will negatively affect the standard deviation of the HRCAP sub-module. Care should be taken to ensure that the 1.2 V supply is clean, and that noisy internal events such as enabling and disabling clock trees have been minimized while using the HRCAP.