SPRUIV4D May 2020 – May 2024

- 1

- Read This First

- 2Introduction

- 3C7000 C/C++ Compiler Options

-

4Basic Code Optimization

- 4.1 Signed Types for Iteration Counters and Limits

- 4.2 Floating-Point Division

- 4.3 Loop-Carried Dependencies and the Restrict Keyword

- 4.4 Function Calls and Inlining

- 4.5 MUST_ITERATE and PROB_ITERATE Pragmas and Attributes

- 4.6 If Statements and Nested If Statements

- 4.7 Intrinsics

- 4.8 Vector Types

- 4.9 C++ Features to Use and Avoid

- 4.10 Streaming Engine

- 4.11 Streaming Address Generator

- 4.12 Optimized Libraries

- 4.13 Memory Optimizations

- 5Understanding the Assembly Comment Blocks

- 6Revision History

3.1 Overview

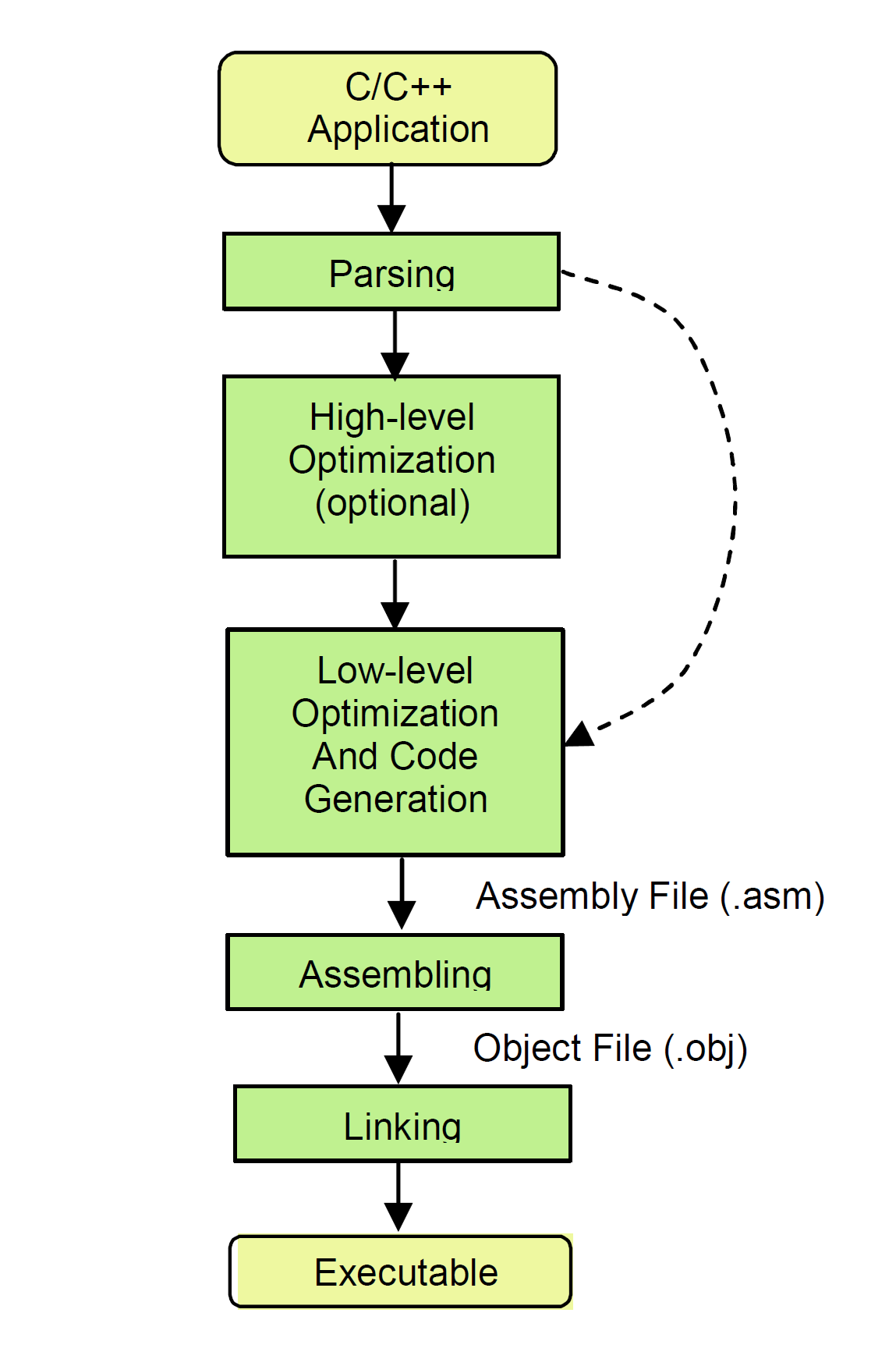

The Texas Instruments C7000 compiler accepts C or C++ source input. When compiling, the compiler proceeds through several stages, as shown in the following figure

Figure 3-1 C7000 Compiler Processing

Stages

Figure 3-1 C7000 Compiler Processing

StagesFirst, the source file is parsed to create a high-level intermediate representation that closely resembles the source language, but is more tailored for optimization transformations.

Files and functions (optionally) compiled with some level of optimization pass through the high-level optimizer, which performs function inlining, loop transformations, and other code optimizations.

Next, the high-level intermediate language is translated into a low-level intermediate language, which closely resembles assembly. The low-level optimizer and code generation pass performs partitioning, register allocation, software pipelining, instruction scheduling, and other optimizations.

The output of the code generation pass is the assembly file, which is assembled into an object file by the assembler and then linked into a library or executable by the linker.