SPRUIW7A October 2020 – February 2022

- Trademarks

- 1Introduction

- 2J7200 EVM Overview

- 3EVM User Setup/Configuration

-

4J7200 EVM Hardware Architecture

- 4.1 J7200 EVM Hardware Top Level Diagram

- 4.2 J7200 EVM Interface Mapping

- 4.3 I2C Address Mapping

- 4.4 GPIO Mapping

- 4.5 Power Supply

- 4.6 Reset

- 4.7 Clock

- 4.8 Memory Interfaces

- 4.9 MCU Ethernet Interface

- 4.10 QSGMII Ethernet Interface

- 4.11 PCIe Interface

- 4.12 USB Interface

- 4.13 Audio Interface

- 4.14 CAN Interface

- 4.15 FPD Interface (Audio Deserializer)

- 4.16 I3C Interface

- 4.17 ADC Interface

- 4.18 RTC Interface

- 4.19 Apple Authentication Header

- 4.20 JTAG Emulation

- 4.21 EVM Expansion Connectors

- 4.22 ENET Expansion Connector

- 5Functional Safety

- 6Revision History

4.12.1 USB 3.1 Interface

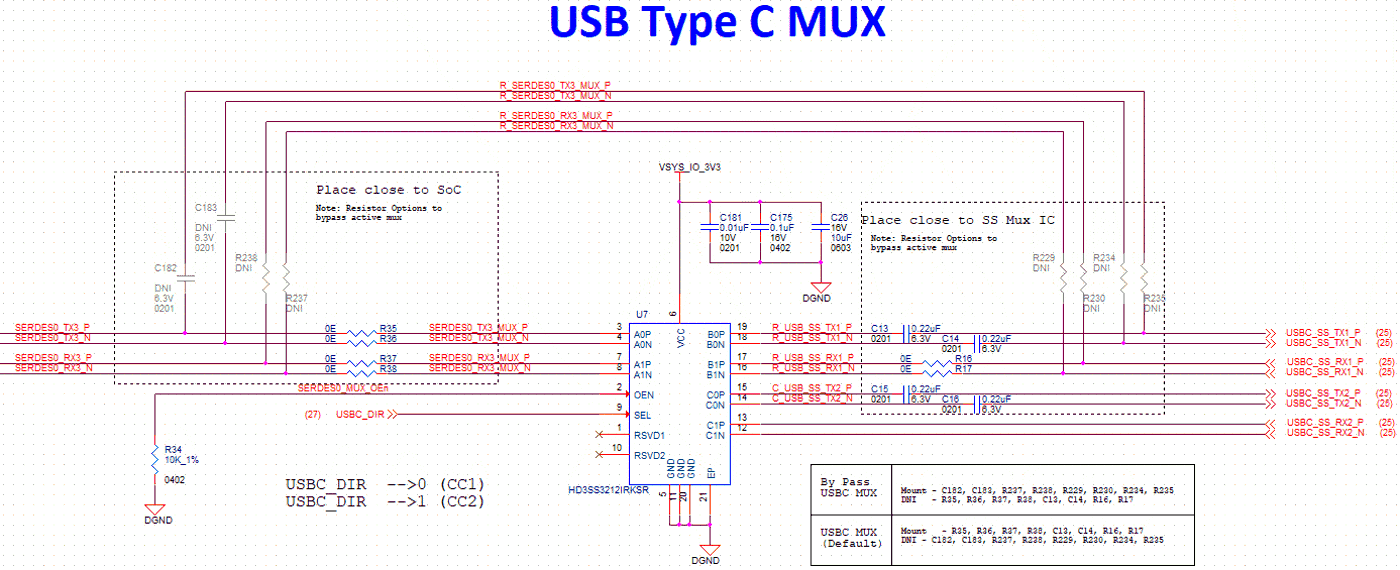

USB Super speed signals from SERDES0 port of J7200 SoC are connected to USB Type C connector (2012670005). A high speed 1:2 Mux HD3SS3212IRKSR is used to support USB Type C lower and upper ports and the mux is enabled by USBC_DIR signal from CC controller.

Figure 4-22 USB SS Mux Circuit

Figure 4-22 USB SS Mux CircuitA CC and PD controller Mfr. Part# TUSB321RWBR and PTPS25830QWRHBTQ1 are used for CC detect, Port mapping and power delivery. This CC controller supports Dual Role Port (DRP), Downstream Facing Port (DFP) and Upstream Facing Port (UFP) modes, In CP board DRP, DFP and UFP modes can be selected through an EVM Configuration dip switch (SW3). The Dip switch settings are given in Table 6.

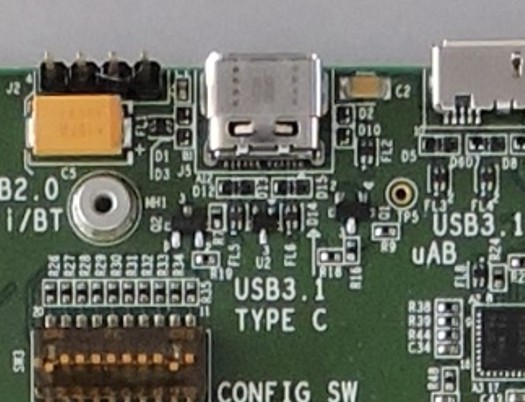

Figure 4-23 USB3.1 Type C Interface

Figure 4-23 USB3.1 Type C Interface The AC coupling capacitors are provided on TX lines of Super speed signals, and common mode filters (MCZ1210DH900L2TA0G) are used at all the differential pairs. ESD protection diodes are provided on all required USB Signals (TPD1E05U06DPY for super speed signals and TPD2E2U06-Q1 for CC pins). TUSB321‘s Current Mode pin is pulled high through 499K resistor to set the Maximum Current Iout to 1.5A.

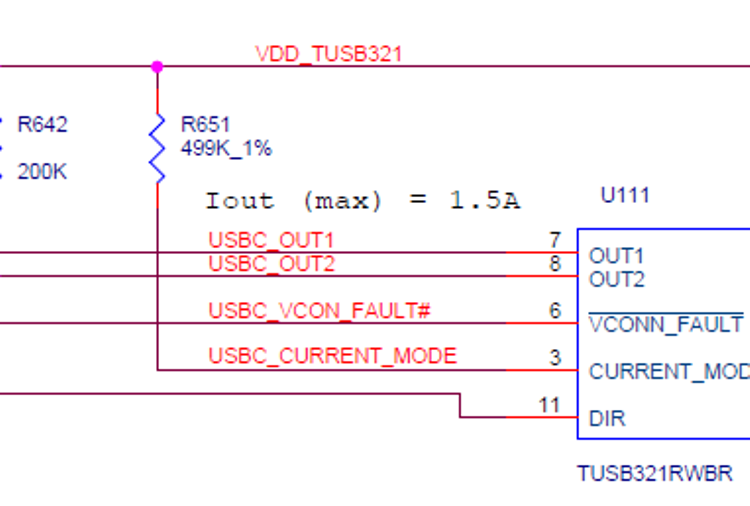

Figure 4-24 USB3.1 Type C Power Delivery

Current Settings

Figure 4-24 USB3.1 Type C Power Delivery

Current SettingsThe control signals for Powerdown and VBUS enable are given from I2C GPIO Expander2 (I2C add: 0x22 - P03) and the SoC DRVVBUS, respectively.