SPRUIW7A October 2020 – February 2022

- Trademarks

- 1Introduction

- 2J7200 EVM Overview

- 3EVM User Setup/Configuration

-

4J7200 EVM Hardware Architecture

- 4.1 J7200 EVM Hardware Top Level Diagram

- 4.2 J7200 EVM Interface Mapping

- 4.3 I2C Address Mapping

- 4.4 GPIO Mapping

- 4.5 Power Supply

- 4.6 Reset

- 4.7 Clock

- 4.8 Memory Interfaces

- 4.9 MCU Ethernet Interface

- 4.10 QSGMII Ethernet Interface

- 4.11 PCIe Interface

- 4.12 USB Interface

- 4.13 Audio Interface

- 4.14 CAN Interface

- 4.15 FPD Interface (Audio Deserializer)

- 4.16 I3C Interface

- 4.17 ADC Interface

- 4.18 RTC Interface

- 4.19 Apple Authentication Header

- 4.20 JTAG Emulation

- 4.21 EVM Expansion Connectors

- 4.22 ENET Expansion Connector

- 5Functional Safety

- 6Revision History

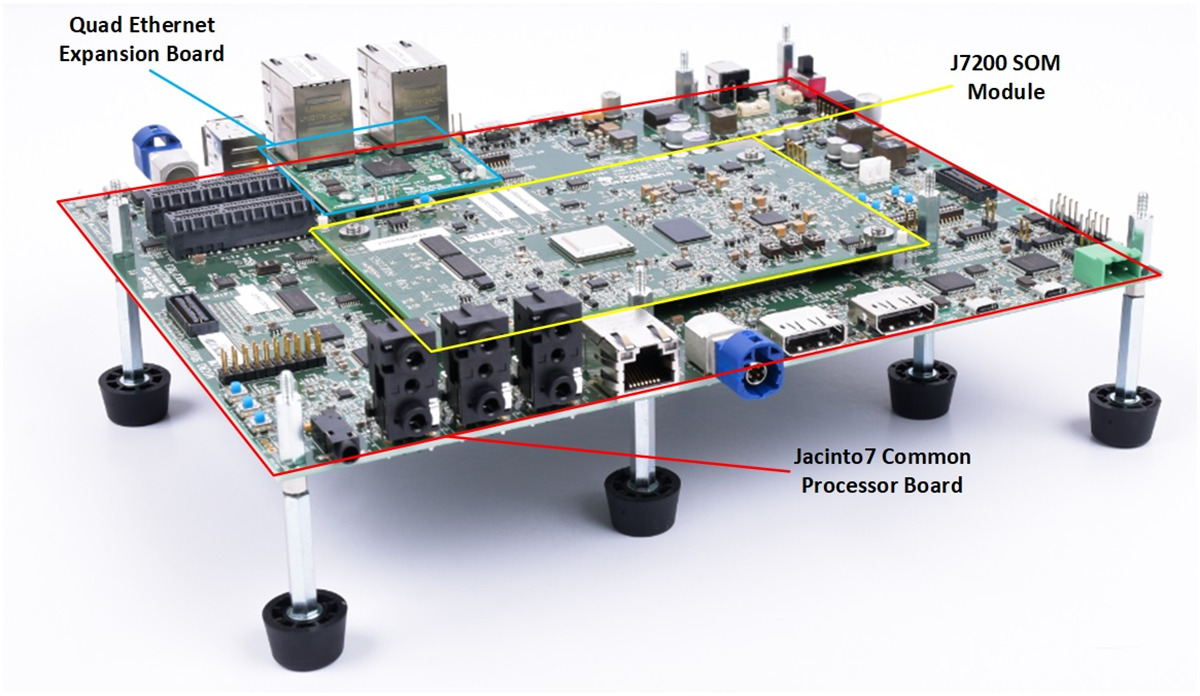

2.1 J7200 EVM Board Identification

Figure 2-3 J7200 EVM Board Identification

(SOM, CPB, QP Ethernet)

Figure 2-3 J7200 EVM Board Identification

(SOM, CPB, QP Ethernet)