SPRUIW7A October 2020 – February 2022

- Trademarks

- 1Introduction

- 2J7200 EVM Overview

- 3EVM User Setup/Configuration

-

4J7200 EVM Hardware Architecture

- 4.1 J7200 EVM Hardware Top Level Diagram

- 4.2 J7200 EVM Interface Mapping

- 4.3 I2C Address Mapping

- 4.4 GPIO Mapping

- 4.5 Power Supply

- 4.6 Reset

- 4.7 Clock

- 4.8 Memory Interfaces

- 4.9 MCU Ethernet Interface

- 4.10 QSGMII Ethernet Interface

- 4.11 PCIe Interface

- 4.12 USB Interface

- 4.13 Audio Interface

- 4.14 CAN Interface

- 4.15 FPD Interface (Audio Deserializer)

- 4.16 I3C Interface

- 4.17 ADC Interface

- 4.18 RTC Interface

- 4.19 Apple Authentication Header

- 4.20 JTAG Emulation

- 4.21 EVM Expansion Connectors

- 4.22 ENET Expansion Connector

- 5Functional Safety

- 6Revision History

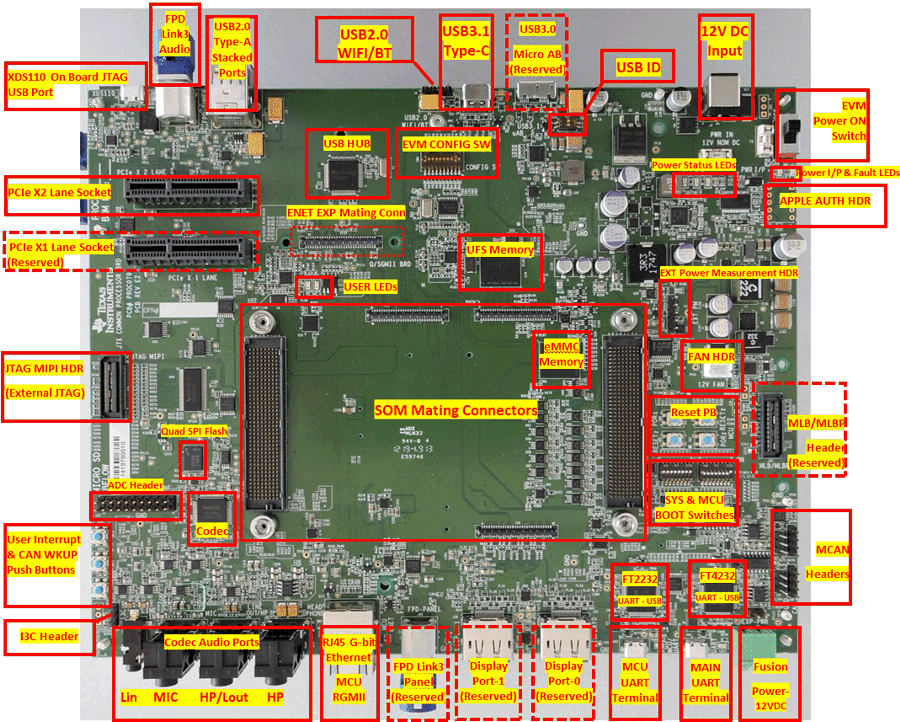

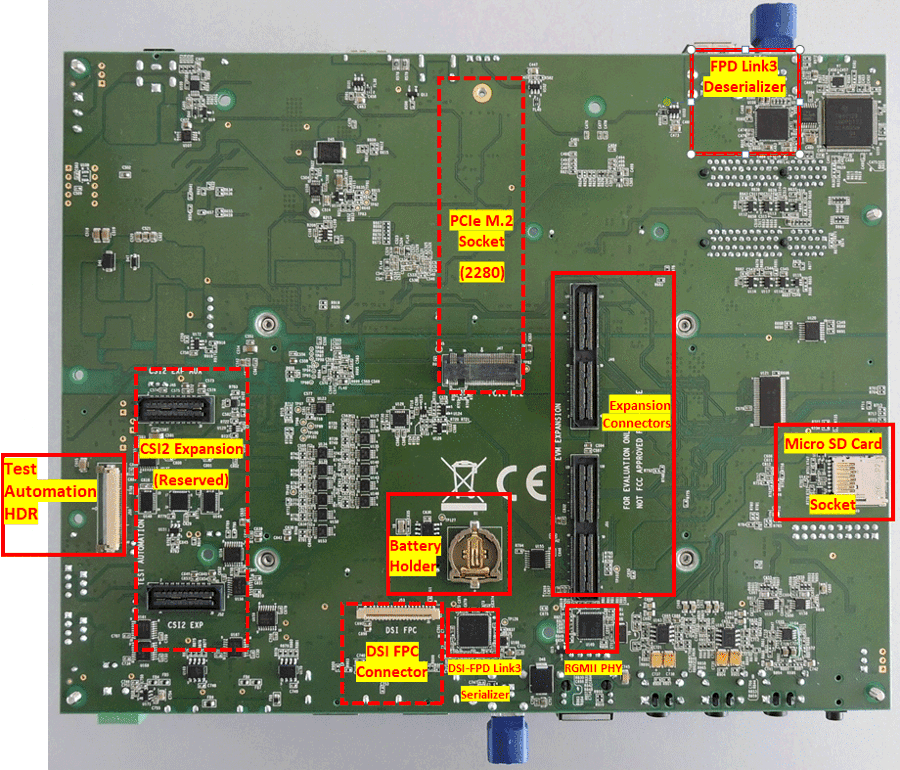

2.3 Jacinto7 Common Processor Component Identification

Figure 2-5 Jacinto7 Common Processor

Component Identification

Figure 2-5 Jacinto7 Common Processor

Component IdentificationBecause the Jacinto7 Common Processor board is used with different SOM boards featuring different Jacinto7 processors with different feature sets, some of the board’s peripherals/interfaces may not be supported. For the J7200 SOM, the following interfaces are not supported:

- USB 3.0 uAB

- Display Port 0

- Display Port 1

- FPD deserializer

- PCIe M.2

- PCIe x1

- DSI interface

- UFS

- MLB

- CSI2