SPRUIY1D November 2020 – August 2024

- 1

- Description

- Features

- 4

- 1Evaluation Module Overview

-

2Hardware

- 2.1 Board Setup

- 2.2 Hardware Description

- 2.3 Connectors

- 2.4 Mechanical Mounting of the PCB

- 3Additional Information

- 4Revision History

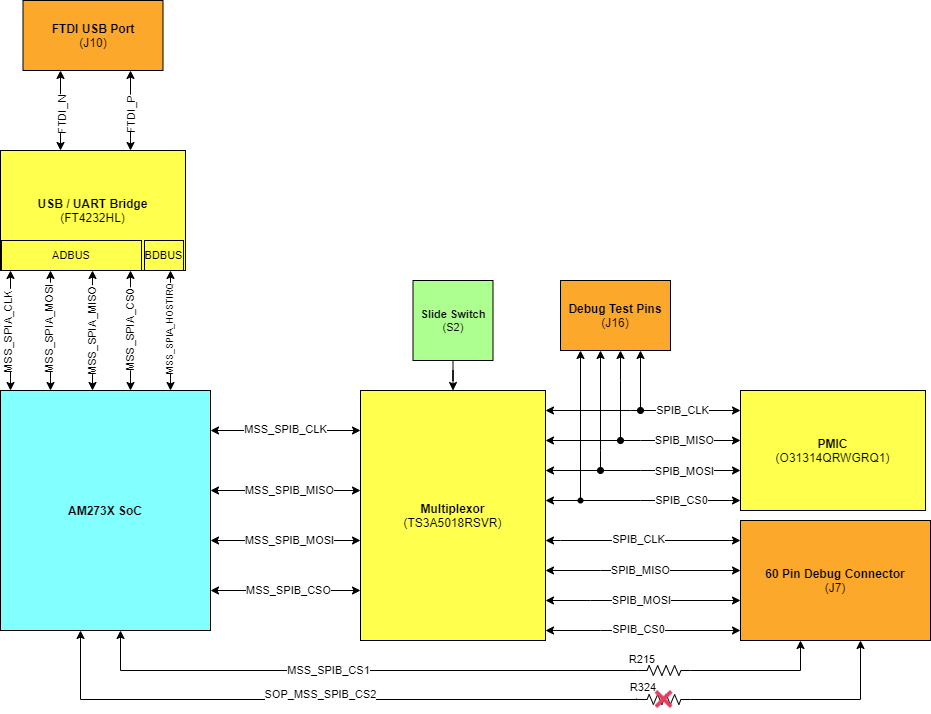

2.2.9 SPI Interface

The EVM supports four SPIs:

- Two main subsystem interfaces:

- MSS_SPIA is accessible through the FTDI USB port (J10) via the FT4232HL UART USB bridge.

- MSS_SPIB is multiplexed out via the

TS3A5018RSVR multiplexor to either the PMIC and debug test pins (J16) or the 60 Pin

Debug Header (J7). The TS3A5018RSVR mutliplexor is driven by S2 which acts as a select

line. When set to 'PMIC_SPI' position, the MSS_SPIB interface is routed to the PMIC

and J16 header. When set to ‘DBG_SPI’, the MSS_SPIB interface is routed to the 60-pin

debug header (J7). The CS1 line of the MSS_SPIB interface bypasses the multiplexor and

is routed directly to the 60 Pin Debug Header.

Figure 2-23 MSS SPI Interface

- Two radar control subsystem

interfaces:

- RCSS_SPIA is routed to the HD front end connector J1.

- RCSS_SPIB is routed to the HD front end connector J11.