SPRUIY9B May 2021 – October 2023

- 1

- Abstract

- Trademarks

- 1Key Features

- 2EVM Revisions and Assembly Variants

- 3Important Usage Notes

-

4System Description

- 4.1 Key Features

- 4.2 Functional Block Diagram

- 4.3 Power-On/Off Procedures

- 4.4

Peripheral and Major Component

Description

- 4.4.1 Clocking

- 4.4.2 Reset

- 4.4.3 Power

- 4.4.4 Configuration

- 4.4.5 JTAG

- 4.4.6 Test Automation

- 4.4.7 UART Interface

- 4.4.8 Memory Interfaces

- 4.4.9 Ethernet Interface

- 4.4.10 USB 3.0 Interface

- 4.4.11 PRU Connector

- 4.4.12 User Expansion Connector

- 4.4.13 MCU Connector

- 4.4.14 Interrupt

- 4.4.15 I2C Interface

- 4.4.16 IO Expander (GPIOs)

-

5Known Issues

- 5.1 Issue 1: LP8733x Max output Capacitance Spec Exceeded on LDO0 and LDO1

- 5.2 Issue 2: LP8733x Output Voltage of 0.9V Exceeds AM64x VDDR_CORE max Voltage Spec of 0.895 V

- 5.3 Issue 3 - SDIO Devices on MMC0 Require Careful Trace Lengths to Meet Interface Timing Requirements

- 5.4 Issue 4 - LPDDR4 Data Rate Limitation in Stressful Conditions

- 5.5 Issue 5 - Junk Character

- 5.6 Issue 6 - Test Power Down Signal Floating

- 5.7 Issue 7 - uSD Boot Not Working

- 6Regulatory Compliance

- 7Revision History

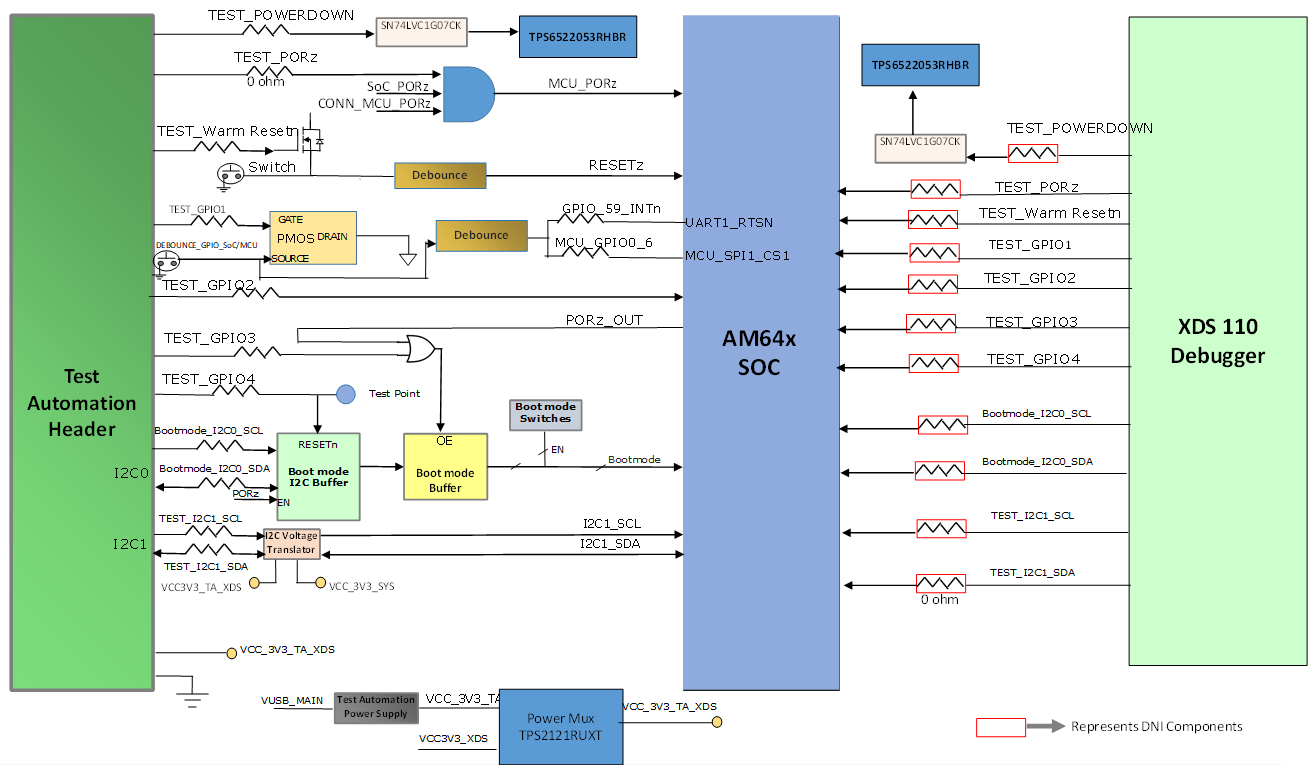

4.4.6 Test Automation

The SKEVM has a 40 pin test automation header (J16) to allow an external controller to manipulate some basic operations like Power Down, POR, Warm Reset, Boot Mode control, etc. The test automation header includes four GPIOs and two I2C interfaces (I2C1, Boot mode I2C0).

The test automation circuit has voltage translation circuits so that the controller is isolated from the IO voltages used by the AM64x. Boot mode for the AM64x must be controlled by either the user using DIP Switches or the test automation header through the I2C IO Expander.

Boot Mode Buffers are used to isolate the Boot Mode controls driven through DIP Switches or I2C IO Expanders. Power to Test Automation Circuit is provided from a Power Mux (TPS2121RUXT) which is having the input supplies VCC3V3_TA supply generated from a dedicated regulator and VCC3V3_XDS generated from an LDO (it is the supply for XDS110 Debugger section). The basic controls of test automation header J16 are as follows. Table 4-14 gives details about test automation header signals.

Optionally, the Test Automation header functionality can be implemented by the XDS110 controller. Hence resistor options (R420, R421, R422, R423, R424, R425, R426, R427, R436, R437, R438 and R439) are provided for Power Down, POR, Warm Reset, Boot Mode controls and GPIO signals. By default these resistors are made as DNI so that an external controller controls the basic operations through the Automation header. Once the firmware for the XDS110 is developed, then mount the above mentioned resistors and DNI the following resistors R380, R381, R382, R383, R384, R385, R386, R432, R433, R434 and R435 to control the basic operations through the XDS110 microcontroller.

Proper Isolation to be provided on Boot Mode signals to allow normal operation. SoC_I2C [1] connected to test automation header to communicate with external controller.

One of the I2C interfaces from Test automation header is connected to the Boot mode buffer to control the boot mode of AM64x and another I2C interface is connected to the I2C1 port of AM64x.

Table 4-14 lists the reset signals routed from test automation header. The boot mode for the AM64x can be controlled by either the user or the test automation header. The boot mode is controlled by the user using two separate 8-positions DIP switches on the board. The switches connect a pull-up resistor to the output of a buffer when the switch is set to ON position. When the switch is off, a weaker pull-down resistor holds the signal low. The output of the buffer is connected to the boot mode pins on the AM64x and the output is enabled when the boot mode is needed during a reset cycle and the input of buffer is connected to output of an I2C buffer set by the test automation circuit.

| Signal | Signal Type | Function |

|---|---|---|

| POWER_DOWN | GPIO | Instructs the EVM to power down all circuits |

| PORZn | GPIO | Creates a PORz to the AM64X |

| WARM_RESETn | GPIO | Creates a RESETz to the AM64X |

| GPIO1 | GPIO | GPIO for communication with AM64X |

| GPIO2 | GPIO | GPIO for communication with AM64X |

| GPIO3 | GPIO | Used to Enable the BOOTMODE Buffer |

| GPIO4 | GPIO | Used to Reset the Boot mode IO Expander |

| Bootmode I2C0 | I2C | Communicates with boot mode I2C buffer |

| I2C1 | I2C | Communicates with AM64x |

If the test automation circuit is going to control the boot mode, then all the switches have to be manually be set to the off position. The pins used for boot mode also have other functions, which is isolated by disabling the boot mode buffer during normal operation. Figure 4-12 shows the test automation signal connection with AM64x.

Figure 4-12 Test Automation Header

Figure 4-12 Test Automation HeaderTest Automation Header signals are optionally connected to the XDS110 microcontroller via zero ohm resistors. By default those resistors are made as DNI.

| TM4C1294 Pin Name | Signal Name |

|---|---|

| PM0 | TEST_POWERDOWN |

| PM1 | TEST_PORZn |

| PM2 | TEST_WARMRESETn |

| PM3 | TEST_GPIO1 |

| PM4 | TEST_GPIO2 |

| PM5 | TEST_GPIO3 |

| PM6 | TEST_GPIO4 |

| PM7 | TEST_POWERDOWN |

| PG0 | TEST_PORZn |

| PG1 | TEST_WARMRESETn |

Table 4-16 lists test automation header’s pin-out and IO direction.

| Pin No. | Signal Name | IO Direction (wrt SoC) |

|---|---|---|

| 1 | VCC3V3_TA | Power (out) |

| 2 | VCC3V3_TA | Power (out) |

| 3 | VCC3V3_TA | Power (out) |

| 4 | NC | NA |

| 5 | NC | NA |

| 6 | NC | NA |

| 7 | DGND | Ground |

| 8 | NC | NA |

| 9 | NC | NA |

| 10 | NC | NA |

| 11 | NC | NA |

| 12 | NC | NA |

| 13 | NC | NA |

| 14 | NC | NA |

| 15 | NC | NA |

| 16 | DGND | Ground |

| 17 | NC | NA |

| 18 | NC | NA |

| 19 | NC | NA |

| 20 | NC | NA |

| 21 | NC | NA |

| 22 | NC | NA |

| 23 | NC | NA |

| 24 | NC | NA |

| 25 | DGND | Ground |

| 26 | TEST_POWERDOWN | Input |

| 27 | TEST_PORZn | Input |

| 28 | TEST_WARMRESETn | Input |

| 29 | NC | NA |

| 30 | TEST_GPIO1 | Bidirectional |

| 31 | TEST_GPIO2 | Bidirectional |

| 32 | TEST_GPIO3 | Input |

| 33 | TEST_GPIO4 | Input |

| 34 | DGND | Ground |

| 35 | NC | NA |

| 36 | SOC_I2C1_TA_SCL | Bidirectional |

| 37 | BOOTMODE_I2C_SCL | Bidirectional |

| 38 | SOC_I2C1_TA_SDA | Bidirectional |

| 39 | BOOTMODE_I2C_SDA | Bidirectional |

| 40 | DGND | Ground |

| 41 | DGND | Ground |

| 42 | DGND | Ground |