SPRUJ66A February 2023 – December 2023

- 1

- Abstract

- Trademarks

- 1EVM Revisions and Assembly Variants

- 2Inside the Box

- 3EMC, EMI, and ESD Compliance

-

4System Description

- 4.1 Key Features

- 4.2 Functional Block Diagram

- 4.3 AM62A Low Power SK EVM Interface Mapping

- 4.4 Power ON/OFF Procedures

- 4.5

Peripheral and Major Component Description

- 4.5.1 Clocking

- 4.5.2 Reset

- 4.5.3 CSI Interface

- 4.5.4 Audio Codec Interface

- 4.5.5 HDMI Display Interface

- 4.5.6 JTAG Interface

- 4.5.7 Test Automation Header

- 4.5.8 UART Interface

- 4.5.9 USB Interface

- 4.5.10 Memory Interfaces

- 4.5.11 Ethernet Interface

- 4.5.12 GPIO Port Expander

- 4.5.13 GPIO Mapping

- 4.5.14 Power

- 4.5.15 AM62A Low Power SK EVM User Setup and Configuration

- 4.5.16 Expansion Headers

- 4.5.17 I2C Address Mapping

- 5Revision History

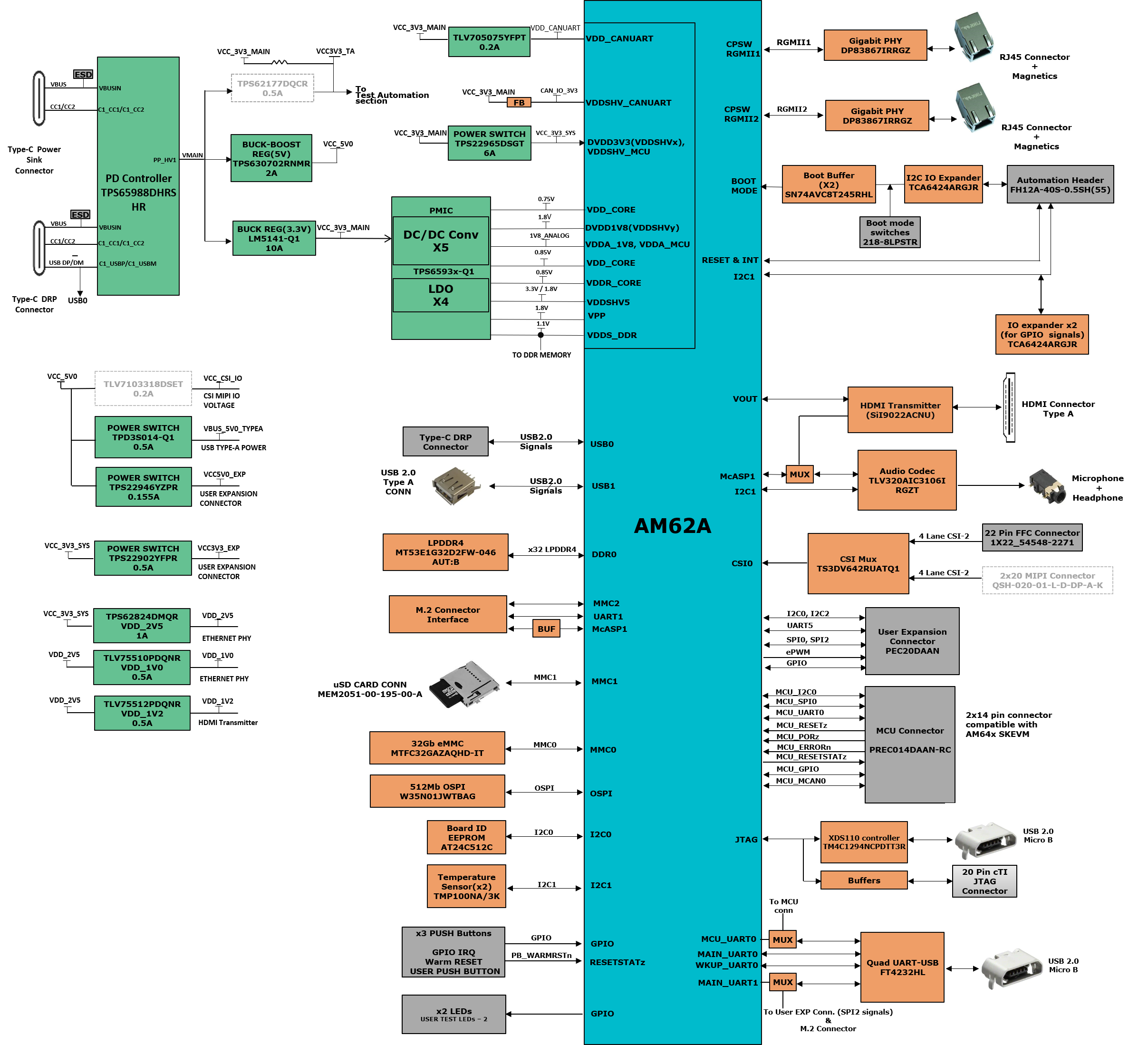

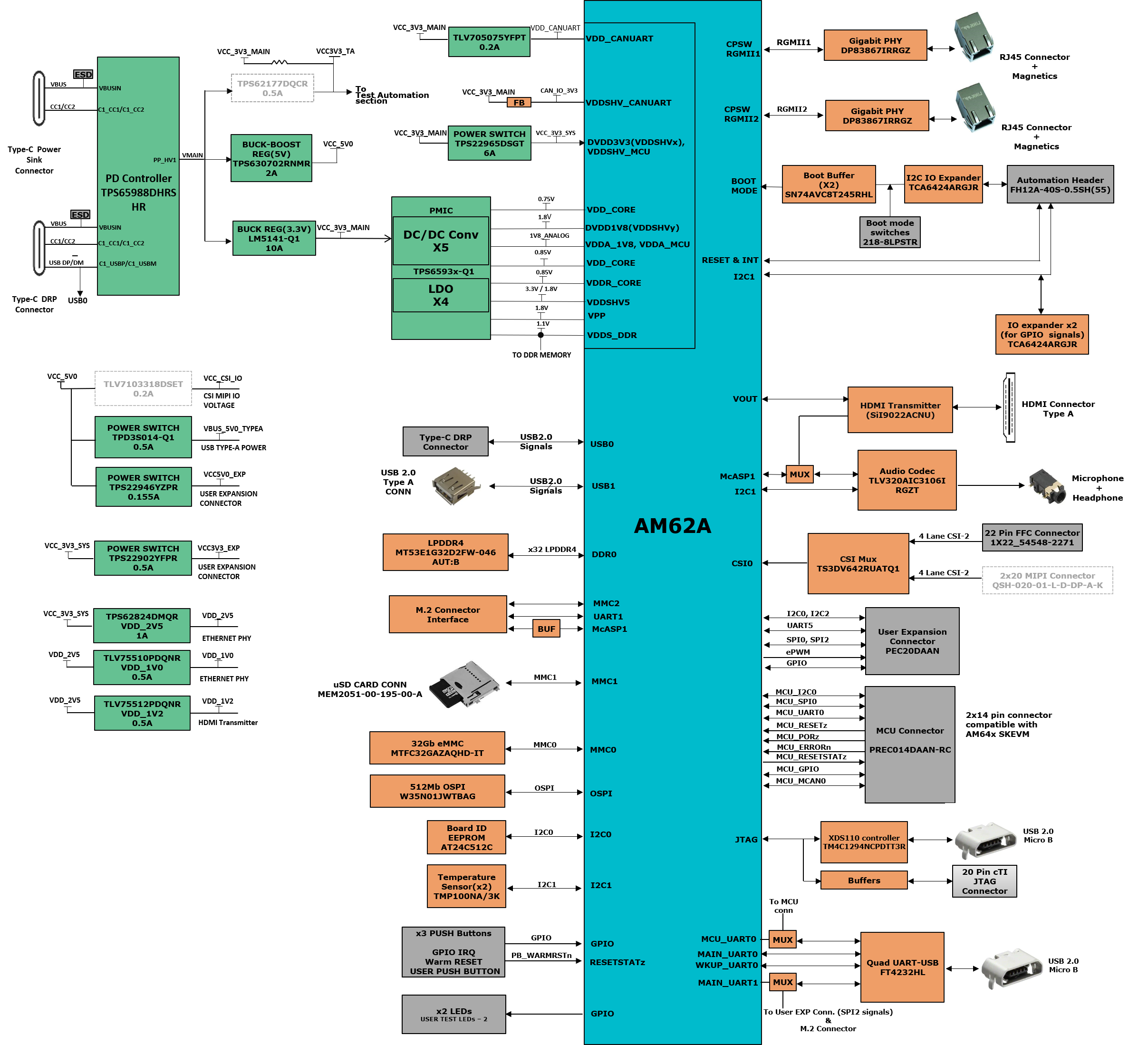

4.2 Functional Block Diagram

The functional block diagram of the AM62A Low Power SKEVM

Board is shown below:

Figure 4-6 Block Diagram - Rev E1 and

E2

Figure 4-6 Block Diagram - Rev E1 and

E2

Figure 4-7 Block Diagram - Rev E3 and A

Figure 4-7 Block Diagram - Rev E3 and A

Figure 4-6 Block Diagram - Rev E1 and

E2

Figure 4-6 Block Diagram - Rev E1 and

E2 Figure 4-7 Block Diagram - Rev E3 and A

Figure 4-7 Block Diagram - Rev E3 and A