SPRUJA2 November 2023

- 1

- Description

- Get Started

- Features

- 5

- 1Evaluation Module Overview

-

2Hardware

- 2.1 Additional Images

- 2.2 Key Features

- 2.3 Interface Mapping

- 2.4 Power ON/OFF Procedure

- 2.5 Clocking

- 2.6 Reset

- 2.7 CSI Interface

- 2.8 OLDI Interface

- 2.9 DSI Interface

- 2.10 Audio Codec Interface

- 2.11 HDMI Display Interface

- 2.12 JTAG Interface

- 2.13 Test Automation Header

- 2.14 UART Interface

- 2.15 USB Interface

- 2.16 Memory Interfaces

- 2.17 Ethernet Interface

- 2.18 GPIO Port Expander

- 2.19 GPIO Mapping

- 2.20 Power

- 2.21 EVM User Setup/Configuration

- 2.22 Expansion Headers

- 2.23 Interrupt

- 2.24 I2C Address Mapping

- 3Hardware Design Files

- 4Compliance Information

- 5Additional Information

2.9 DSI Interface

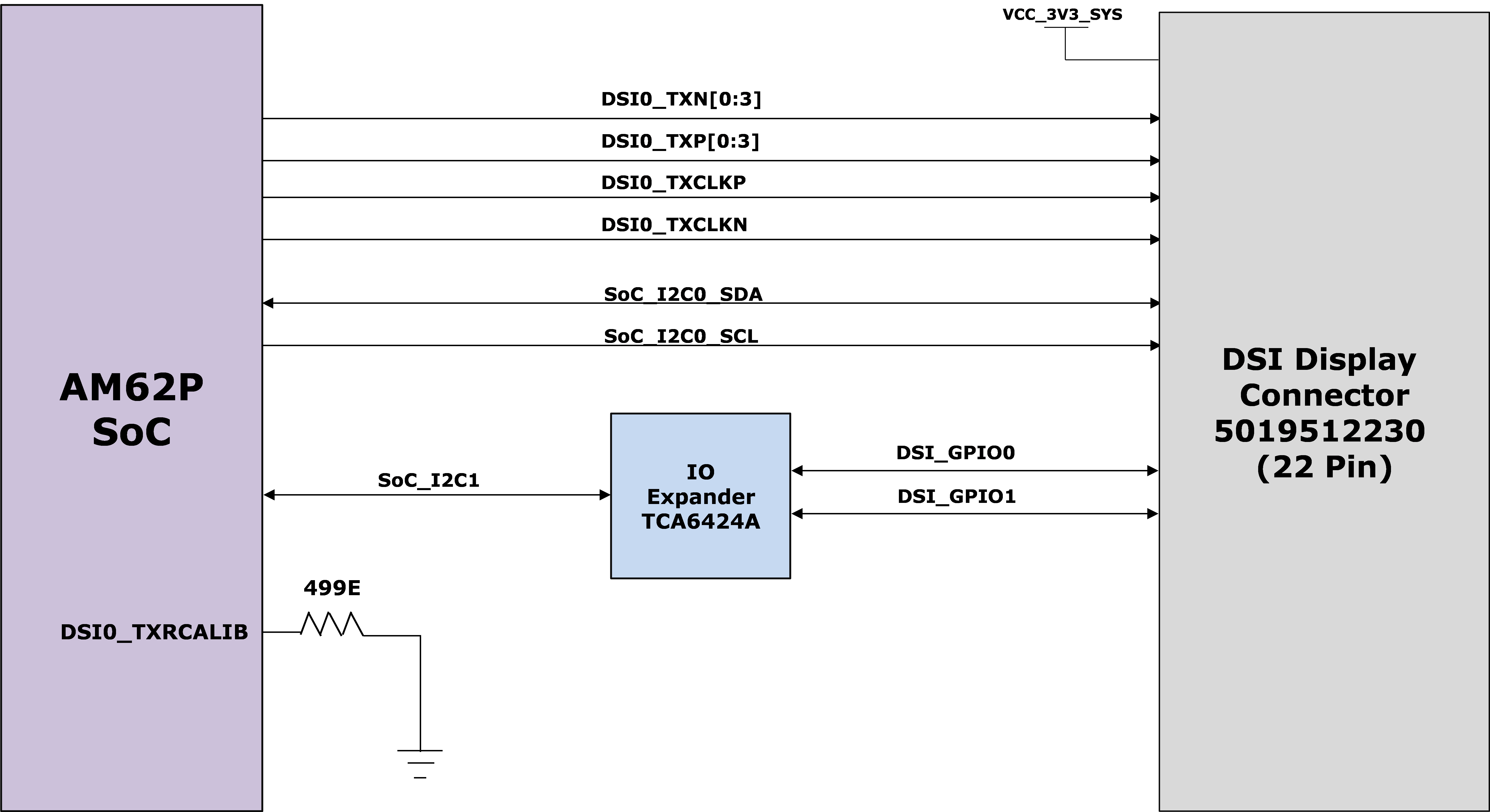

The DSI Display interface of the AM62P SOC is connected to a 22-pin display connector (J25) Mfr Part# 5019512230 from Molex. The AM62P SK EVM supports 4 DSI-TX lanes for high-speed video link and low power command link with resolutions up to 3840x1080p. Apart from these four lanes, the 22-pin connector is provided with a 3.3V supply with sourcing capability until 500 mA, I2C0 for any pre-initializations and two GPIO’s for handling interrupt and reset to the interfacing display.

Figure 2-9 DSI Interface

Figure 2-9 DSI InterfaceTable 2-6 DSI Display Connector (J25)

Pinout

| Pin No. | Signal |

|---|---|

| 1 | VCC_3V3_SYS |

| 2 | SOC_I2C0_SDA |

| 3 | SOC_I2C0_SCL |

| 4 | DGND |

| 5 | DSI_INTN# |

| 6 | DSI_RESETN |

| 7 | DGND |

| 8 | DSI_TX3_P |

| 9 | DSI_TX3_N |

| 10 | DGND |

| 11 | DSI_TX2_P |

| 12 | DSI_TX2_N |

| 13 | DGND |

| 14 | DSI_TXCLK_P |

| 15 | DSI_TXCLK_N |

| 16 | DGND |

| 17 | DSI_TX1_P |

| 18 | DSI_TX1_N |

| 19 | DGND |

| 20 | DSI_TX0_P |

| 21 | DSI_TX0_N |

| 22 | DGND |