SPRUJA2 November 2023

- 1

- Description

- Get Started

- Features

- 5

- 1Evaluation Module Overview

-

2Hardware

- 2.1 Additional Images

- 2.2 Key Features

- 2.3 Interface Mapping

- 2.4 Power ON/OFF Procedure

- 2.5 Clocking

- 2.6 Reset

- 2.7 CSI Interface

- 2.8 OLDI Interface

- 2.9 DSI Interface

- 2.10 Audio Codec Interface

- 2.11 HDMI Display Interface

- 2.12 JTAG Interface

- 2.13 Test Automation Header

- 2.14 UART Interface

- 2.15 USB Interface

- 2.16 Memory Interfaces

- 2.17 Ethernet Interface

- 2.18 GPIO Port Expander

- 2.19 GPIO Mapping

- 2.20 Power

- 2.21 EVM User Setup/Configuration

- 2.22 Expansion Headers

- 2.23 Interrupt

- 2.24 I2C Address Mapping

- 3Hardware Design Files

- 4Compliance Information

- 5Additional Information

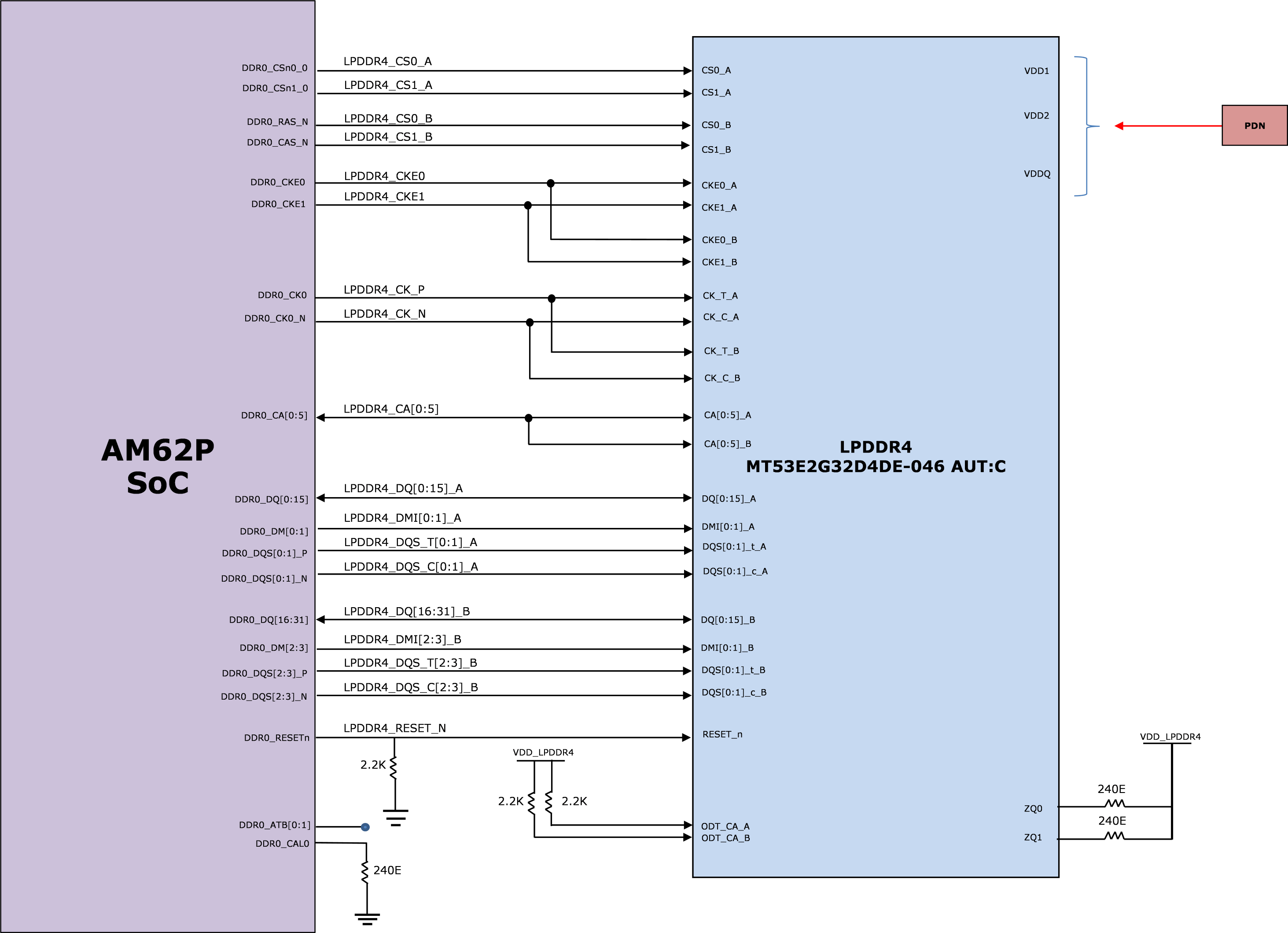

2.16.1 LPDDR4 Interface

AM62P SK EVM houses Micron’s (MT53E2G32D4DE-046 AUT:C) dual Rank dual Die 8GB, 32-bit wide LPDDR4 memory supporting data rates up to 3200 Mb/s per pin. The LPDDR4 memory is placed routed to the DDR0 group of SOC to support point to point communication.

The LPDDR4 memory requires 1.8V for the core supply, thus reducing power demand. The I/O’s are supplied from a 1.1V supply output from the PMIC. LPDDR4 reset (active low) controlled by the AM62P SOC is pulled down to set the default active state. The provision for mounting a pull up resistor is also provided.

Figure 2-17 LPDDR4 Interface

Figure 2-17 LPDDR4 Interface