SPRUJG2 December 2024 AM62D-Q1

- 1

- Description

- Get Started

- Features

- 5

- 1Evaluation Module Overview

-

2Hardware

- 2.1 Additional Images

- 2.2 Key Features

- 2.3 Power Requirement

- 2.4 Setup and Configuration

- 2.5 Power ON/OFF Procedures

- 2.6 Interfaces

- 2.7 Power

- 2.8 Clocking

- 2.9 Reset

- 2.10 CPLD Mapping

- 2.11 Audio Expansion Connectors (Headers)

- 2.12 Interrupt

- 2.13 I2C Address Mapping

- 3Hardware Design Files

- 4Compliance Information

- 5Additional Information

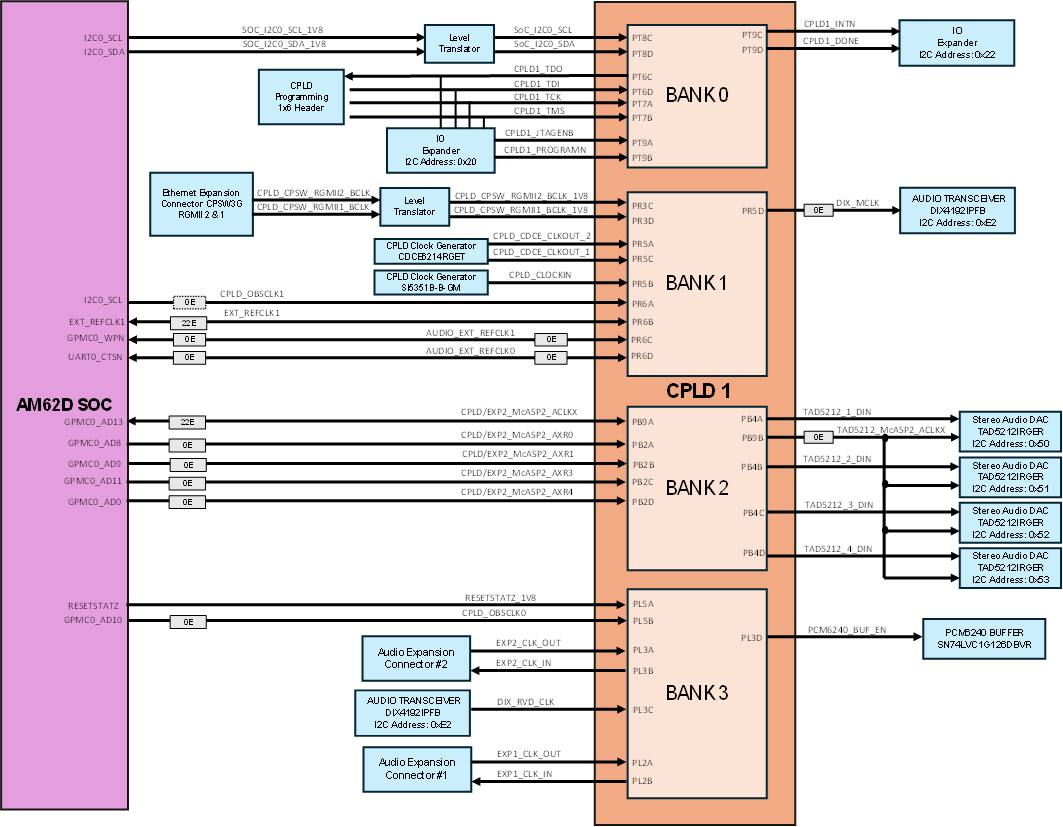

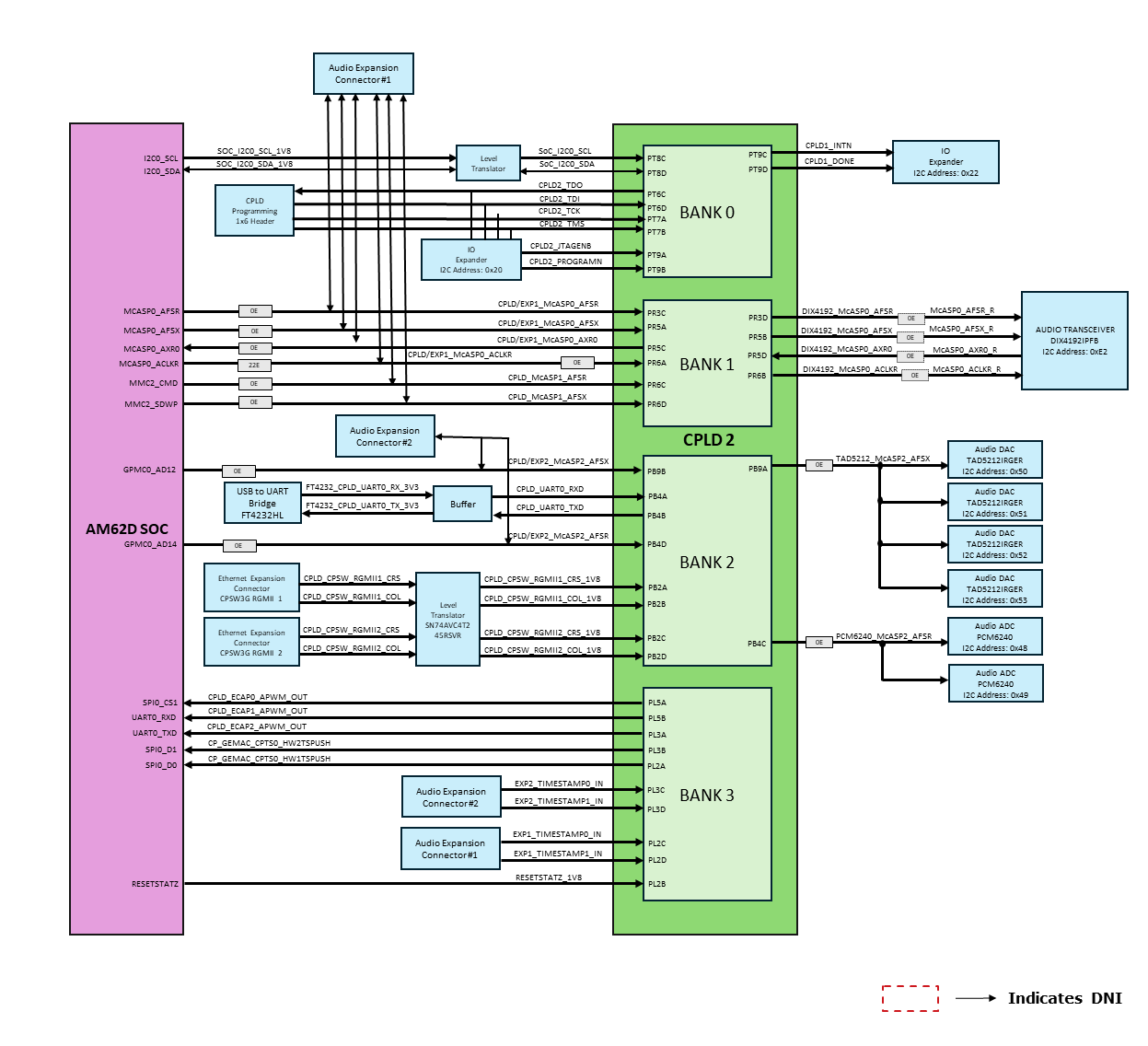

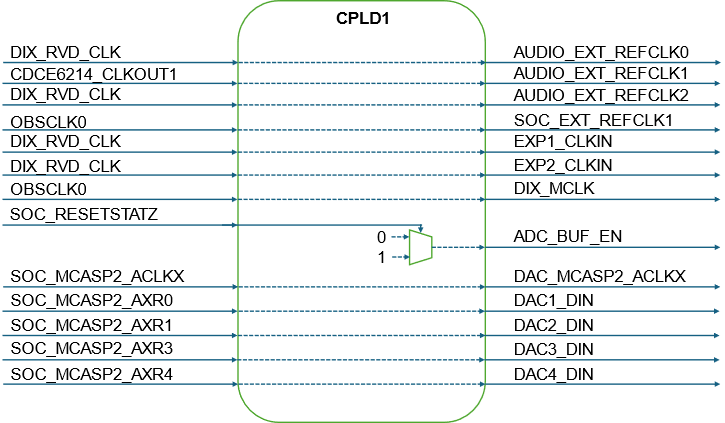

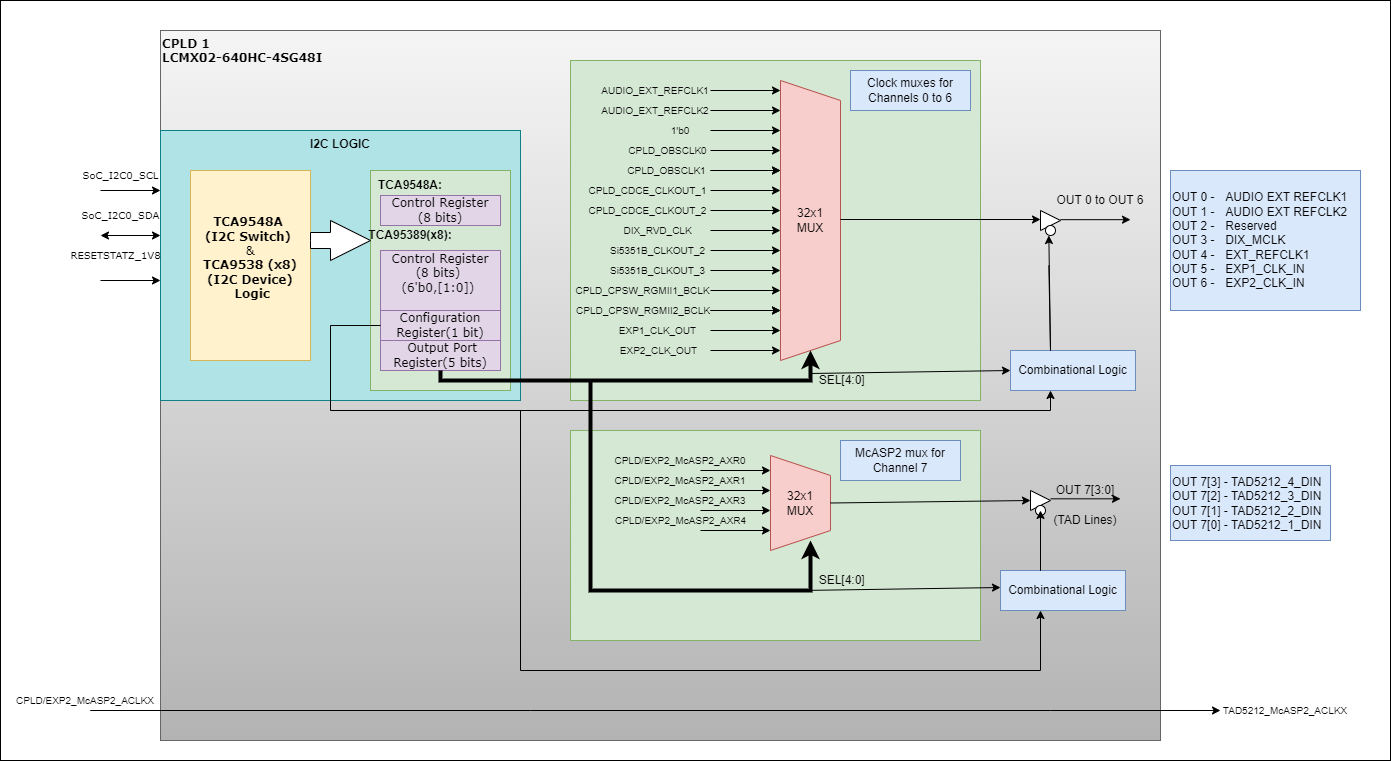

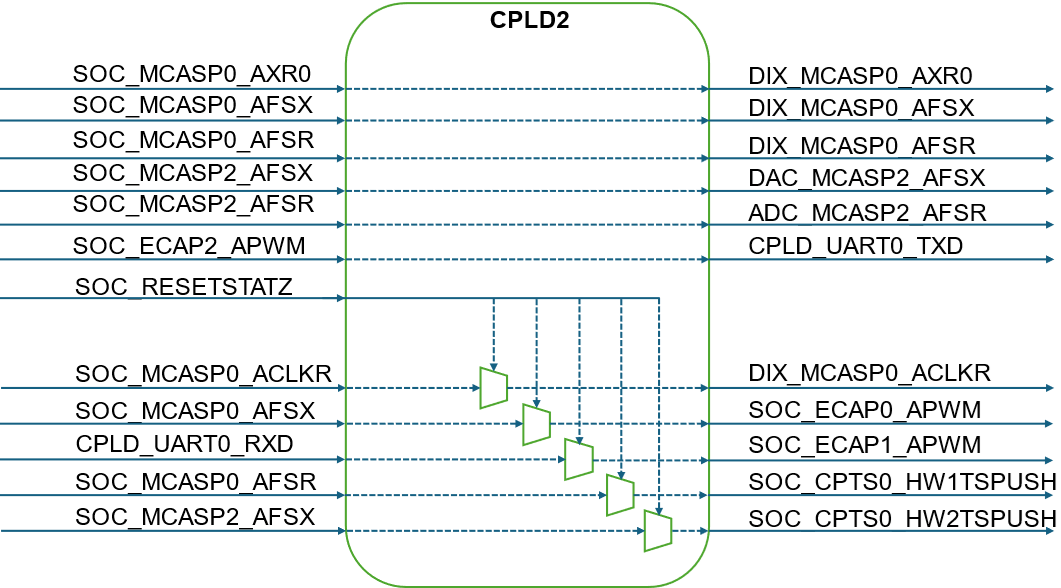

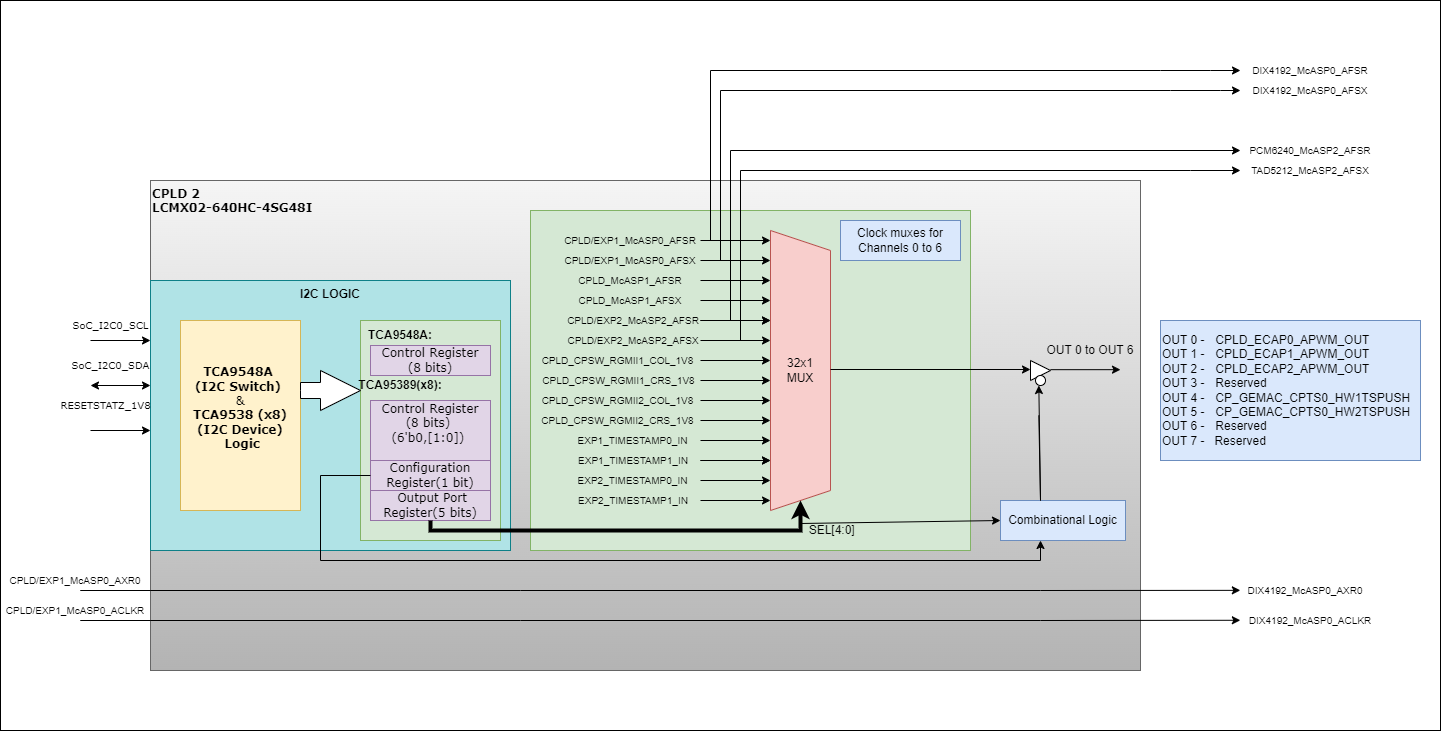

2.10 CPLD Mapping

The AM62D Audio EVM supports 2x CPLDs manufacturer part number LCMXO2-640HC-1SG32I for the Mux/Demux of low frequency audio clocks (<30MHz) and the CPLDs are programmed in buffer logic for audio signals from the SoC to On-board Audio peripheral devices.

The CPLD requires 3.3V for Core (VCC) and VCCIO0 and 1.8V for other I/Os (VCCIO1, VCCIO2 & VCCIO3). 2x 1x6 HDR manufacturer part number 61300611121 are installed for JTAG programming.

Figure 2-24 CPLD1 Block Diagram

Figure 2-24 CPLD1 Block Diagram Figure 2-25 CPLD2 Block Diagram

Figure 2-25 CPLD2 Block DiagramThe current AM62D Audio EVM has CPLD mapping as shown below.

CPLD1 Configuration E1

CPLD1 Configuration E1

Figure 2-26 CPLD1 Pin Mapping

Figure 2-26 CPLD1 Pin MappingCPLD2 Configuration E1

CPLD2 Configuration E1

Figure 2-27 CPLD2 Pin Mapping

Figure 2-27 CPLD2 Pin Mapping