SPRUJG2 December 2024 AM62D-Q1

- 1

- Description

- Get Started

- Features

- 5

- 1Evaluation Module Overview

-

2Hardware

- 2.1 Additional Images

- 2.2 Key Features

- 2.3 Power Requirement

- 2.4 Setup and Configuration

- 2.5 Power ON/OFF Procedures

- 2.6 Interfaces

- 2.7 Power

- 2.8 Clocking

- 2.9 Reset

- 2.10 CPLD Mapping

- 2.11 Audio Expansion Connectors (Headers)

- 2.12 Interrupt

- 2.13 I2C Address Mapping

- 3Hardware Design Files

- 4Compliance Information

- 5Additional Information

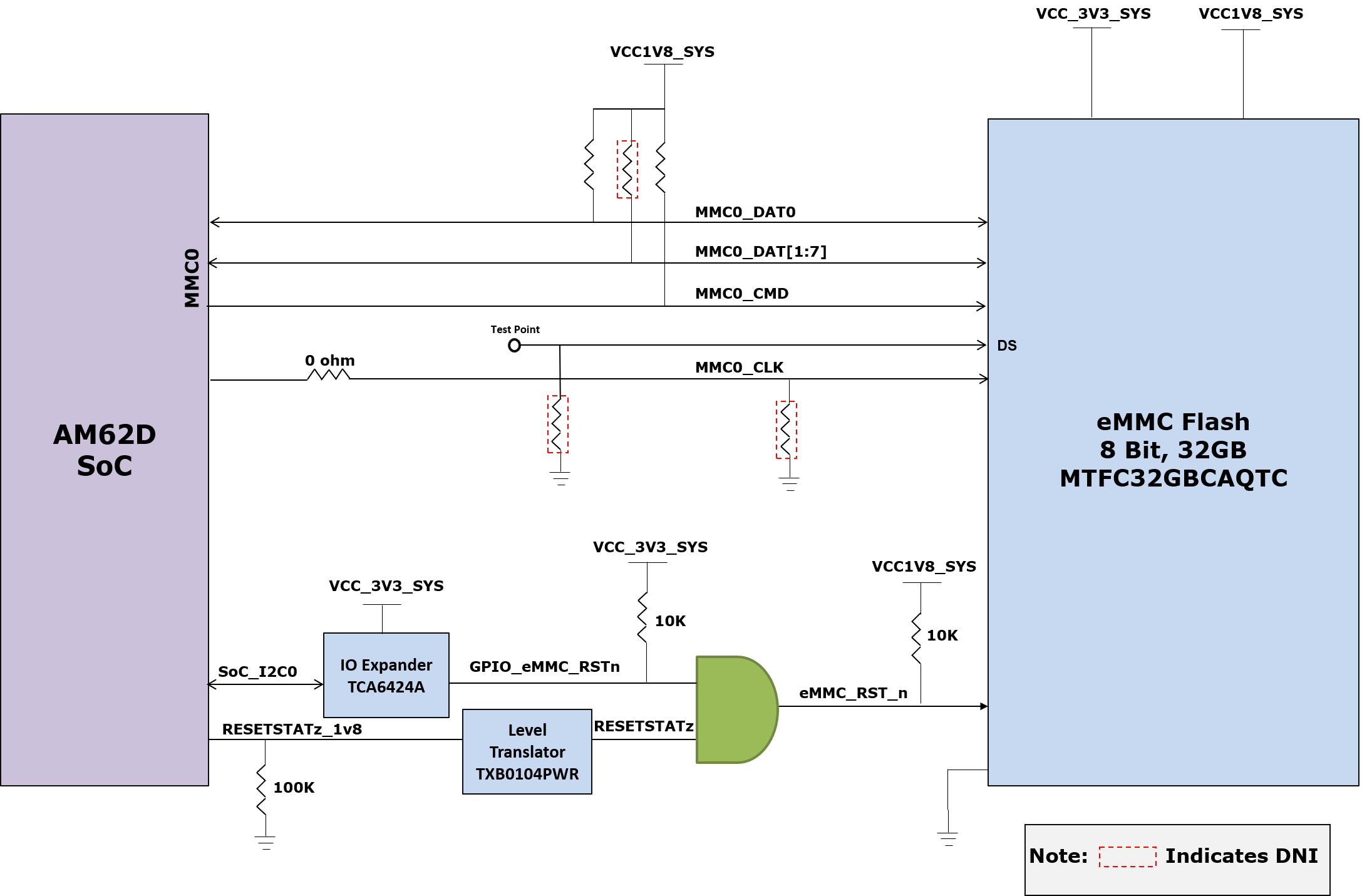

2.6.7.3.1 MMC0 - eMMC Interface

The EVM board contains 32GB of eMMC flash memory from Micron Part # MTFC32GBCAQTC connected to MMC0 port of the AM62D SoC.

The data bus from the flash memory is connected to 8 bits of the MMC0 interface supporting HS400 double data rates up to 200MHz. The Micron eMMC is a communication and mass data storage device that includes a Multimedia Card (MMC) interface and a NAND Flash component. Option to mount external pull up resistors are provided on DAT[7:1] to prevent bus floating and series resistor is provided for CLK signal close to SoC pad to match the characteristic impedance of PCB.

The eMMC device requires two power supplies, 3.3V for NAND memory and 1.8V for the eMMC interface. The MMC0 interface I/Os of the SoC is powered by the VDDSHV4 power domain, which is connected to 1.8V I/O supply.

The eMMC device requires active low reset from host. By default, the RST_n signal is temporarily disabled in the device. The host must set ECSD register byte 162, bits[1:0] to 0x1 to enable this functionality before the host can use it. The External Reset is provided by ANDing RESETSTATz from SoC and a GPIO from I/O Expander. A pull up is provided on GPIO pin to set the default active state.

Figure 2-14 eMMC Interface Block Diagram

Figure 2-14 eMMC Interface Block Diagram