SSZT544 february 2019

Having stumbled upon this blog post, I’m assuming that you know the importance of having a voltage supervisor in your electronic design and are wondering how to implement and design with these different output topology types. Don’t worry! You came to the right post. but before I explain the different output topologies, I want to reiterate the importance of having a voltage supervisor, as many engineers are not familiar with this device.

Output Configurations

Think of a supervisor as an analog-to-digital converter. It senses a supply voltage (analog) and provides a flag (either the RESET or SENSEOUT pin), which is a digital signal. The digital signal output can be in either an open-drain or push-pull topology.

The Open-drain Output Topology

Here are some things to consider when designing with the open-drain output topology:

- Open-drain outputs provide flexibility because they can pull up to any voltage (within absolute maximum) to comply with the logic of the load, rather than pulling the output up to the supervisor’s supply voltage or sense voltage. A pull-up resistor properly limits the current and maintains the low-level output voltage (VOL) and high-level output voltage (VOH) specifications.

- It’s possible to wire-OR together multiple open-drain outputs through a single pull-up resistor. The open-drain output can also pull up to any voltage that complies with the logic of the load giving flexibility to a designer.

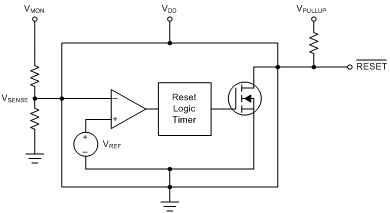

- The pull-up resistance cannot be too low such that the current through the open drain damages the supervisor. When the internal n-channel metal-oxide semiconductor (NMOS) (Figure 1) is on, current from the pull-up resistor will go through the NMOS and be pulled to ground. You should select the pull-up resistance based on two criteria. The first criteria is the supervisor’s recommended maximum reset or sense current, called IRESET or ISENSE, which is specified in the data sheet. If the current being pulled to ground is higher than IRESET, the supervisor’s internal NMOS could be damaged. The second criteria is based on the VOL requirements of the load that the output of the voltage supervisor connects to. Lower pull-up resistors will also result in higher VOL due to the increase in reset/sense current.

- The pull-up resistance cannot be too high such that the leakage current through the open-drain resistor at high temperatures falls outside the VOH specification found in the data sheet. By increasing the pull-up resistance, VOH decreases due to the smaller reset or sense current, causing a smaller voltage drop across the internal metal-oxide semiconductor field-effect transistor (MOSFET).

- The output rise time is decided by the pull-up resistance and the output board parasitic capacitance. For faster rise times, use smaller pull-up resistances.

- The supervisor’s quiescent current (Iq) does not include the current through the pull-up resistor. If the pull-up voltage is pulled from the supply, the total system Iq will increase, as supply current will also go through the pull-up resistor. If the pull-up voltage connects to another source, the system Iq will equal the supervisor Iq from the data sheet. Since the pull-up voltage can connect to different supplies, the Iq specification of the supervisor does not account for the additional output current resulting from the use of a common supply.

- An open-drain output configuration requires an additional component, a pull-up resistor, connected from the output to a power supply. Without the pull-up resistor, the outputs are undefined when the internal NMOS turns off, as there will be no power supply to pull from.

- The open-drain output can change with the output pull-up supply, and any transient coupling will depend on the pull-up resistance used. A higher pull-up resistance can minimize the effects of transients from the output pull-up supply.

Figure 1 The Open-drain Output Uses an Internal N-MOSFET

Figure 1 The Open-drain Output Uses an Internal N-MOSFETThe Push-pull Topology

Here are some things to consider when designing with the push-pull output topology:

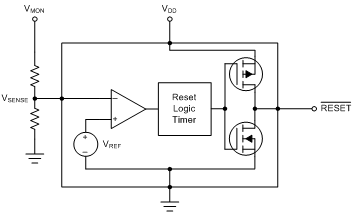

- The output of a push-pull configuration toggles between the supervisor’s supply voltage and ground, with no external pull-up resistance required. Notice how the output in Figure 2 does not use a resistor like in Figure 1, and how Vpullup is not present in Figure 2. Vdd and ground are toggled via the 2 MOSFETS.

- The voltage at the output of a push-pull configuration can never go beyond the supervisor’s voltage supply by more than 0.3V, because the body diodes can turn on and damage the device. The body diode will take excessive current in forward bias mode.

- The quiescent current of the supervisor accounts for the current through the external resistors that can be connected at the output of the supervisor.

- It’s not possible to wire-OR together push-pull outputs like with the open-drain output topology.

- Push-pull outputs are a good fit for high-speed applications because the push-pull output does not have the additional delay that the pull-up resistor causes in the open-drain topology.

Figure 2 In the Push-pull Output Topology, a P-channel MOS (PMOS) and NMOS Connect Together, Similar to an Inverter

Figure 2 In the Push-pull Output Topology, a P-channel MOS (PMOS) and NMOS Connect Together, Similar to an InverterHow to Identify Active Low and Active High

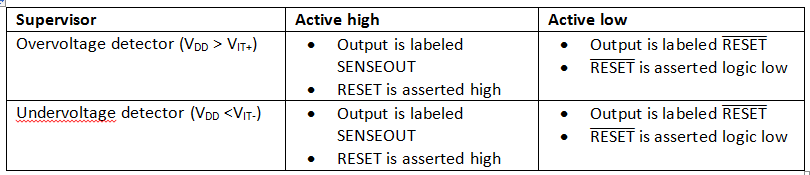

Different types of supervisors monitor under and overvoltage conditions and provide RESET/FLAG/POWERGOOD/SENSEOUT in an active-low or active-high output topology. “SENSEOUT” and “POWERGOOD” labeled pins are active when the supervisor senses the supply voltage is in normal operating condition, whereas a “RESET” labeled pin is active when the supervisor senses the supply voltage is in a fault (under- or overvoltage) condition.

An overvoltage active-high supervisor means that whenever the supply crosses VIT+, signaling an overvoltage condition, RESET activates to logic high.

Table 1 can help you identify the different supervisors.

|

Now that you know more about the different output topologies, you are one step closer to selecting the correct supervisor for your system. Check out TI’s quick search tool to help you find one.

Additional Resources

- Watch the video to learn more about these different output topologies and their use cases.

- Watch the Voltage Supervisors 101 training series.

- Read the two-part blog post series: