SSZTB84 june 2016

So often with a complex processor selection, initial engineering evaluations are focused on performance and cost. However, reliability engineers at industrial equipment manufacturers look at a whole set of different product specifications; those focused on avoiding and managing such errors. Exceeding stringent Failures in Time (FIT) rates - the inverse of Mean Time before Failure (MTBF), for certain applications such as aerospace, military and industrial factory automation are simply unacceptable.

With today’s complex systems engineers must not only focus on embedded solutions that meet cost and performance goals, but devices that will help to assure overall end equipment reliability requirements. While integrated circuits have enabled quantum leaps in performance, size, and overall cost of embedded systems, the reliance on various memory elements and employment of small-geometry silicon process technologies introduce reliability challenges due to the potential for permanent and transient errors.

The integration of a plethora of memory elements into System-on-Chip (Soc) solutions help improve end application size, weight, power and bill of material (BOM)but costs significantly more. With memory being especially sensitive transient errors, the SoC in todays embedded systems often carries the lion’s share of failure potential. Even commonly used peripherals like PCIe and USB include memory elements. Consider a factory automation floor with hundreds of controllers, each with multiple processor SoCs inside and you can start to get the picture of just how important reliability is for production efficiency and cost. Factory line down time is simply unacceptable.

We have been focusing on measuring and improving on reliability for integrated circuits for some time and maintain and utilize a formal process for designing integrated circuits for high reliability.

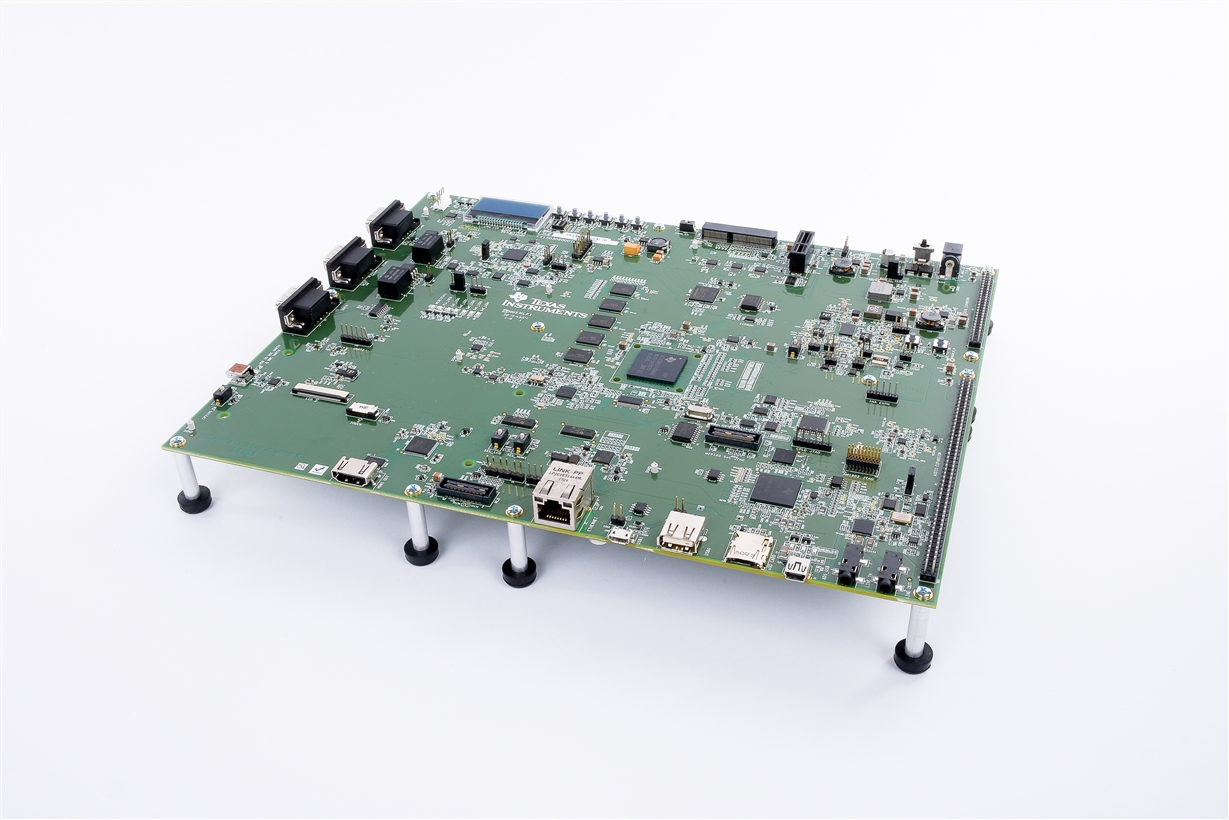

Our latest DSP + ARM processor system-on-chip SoC exemplifies the measures we have taken to improve reliability. The 66AK2G02 processor is designed for real-time processing applications such as industrial motor control, factory communications and home and professional audio and was developed within this reliability process to meet industry reliability standards. Some key features include:

- A 600 MHz C666x DSP and ARM® Cortex® A-15

- Two PRU-ICSS units

- A host of internal memory and range of communication peripherals

- ECC memory

- Designed for MTBF greater than 400 years

Because today's processor functionality and performance relies so much on internal and external memory, it is also important to focus on managing transient errors that can affect a variety of memory types. Error Correcting Codes (ECC), parity bits, and Cyclic Redundancy Checks (CRC) were employed to detect and/or correct bit errors significantly reducing the SER across the device. The ECC method used in 66AK2Gx processor is Single Error Correction and Dual Error Detection (SECDED). Using SECDED, a single bit error is detected and corrected in hardware. For dual bit errors, the errors are detected and the appropriate processor is signaled in the device to take action on the dual bit error.

Learn more about reliability and 66AK2G02 processor :