SWRU613A July 2023 – August 2024 AWRL1432 , IWRL1432

- 1

- Description

- Get Started

- Features

- 5

- 1Evaluation Module Overview

-

2Hardware

- 2.1 XWRL1432BOOST Antenna

- 2.2 EVM Mux Block Diagram

- 2.3 Switch Settings

- 2.4 LEDs

- 2.5 Connectors

- 2.6 USB Connector

- 2.7 DCA1000 HD Connector

- 2.8 Booster Pack Connector for the LaunchPad Connectivity

- 2.9 CANFD Connector

- 2.10 LIN PHY Connection

- 2.11 I2C Connections

- 2.12 XDS110 Interface

- 2.13 Flashing the Board

- 2.14 DCA1000EVM Mode

- 2.15 PCB Storage and Handling Recommendations:

- 3Software

- 4Hardware Design Files

- 5Additional Information

- 6References

- 7Revision History

2.14.1 RDIF Interface for Raw ADC Capture

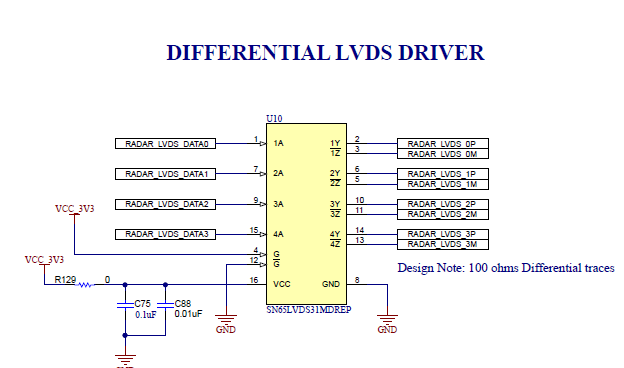

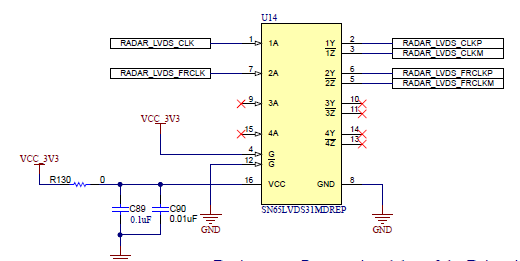

The xWRL1432 doesn’t have LVDS I/Os, mainly to reduce the overall power consumption of the SOC. However, the DCA1000 board needs LVDS signals on the clock and data interface for raw ADC capture. For that reason CMOS to LVDS converters are used on the board as shown below. The data capture interface uses RDIF (Radar Data interface) for transferring the data between mmWave device and DCA1000 capture card. There is no change needed in the DCA1000 capture card for this purpose, however a new low power mmWave studio needs to be used for this purpose. The low power mmWave studio interprets the RDIF interface and provides a raw ADC data visualization platform for further signal processing.

Figure 2-25 DCA1000 CMOS TO LVDS Conversation for Data Lines

Figure 2-25 DCA1000 CMOS TO LVDS Conversation for Data Lines Figure 2-26 DCA1000 CMOS TO LVDS Conversation for Clock and Control Lines

Figure 2-26 DCA1000 CMOS TO LVDS Conversation for Clock and Control Lines