SWRU622 August 2024 AWRL1432 , AWRL6432 , IWRL1432 , IWRL6432 , IWRL6432AOP

- 1

- Trademarks

- 1Introduction

- 2Basic Bootloader Flow

- 3Secondary Bootloader

- 4Warm Reset

- 5Relevant Registers

5.2 PC Registers

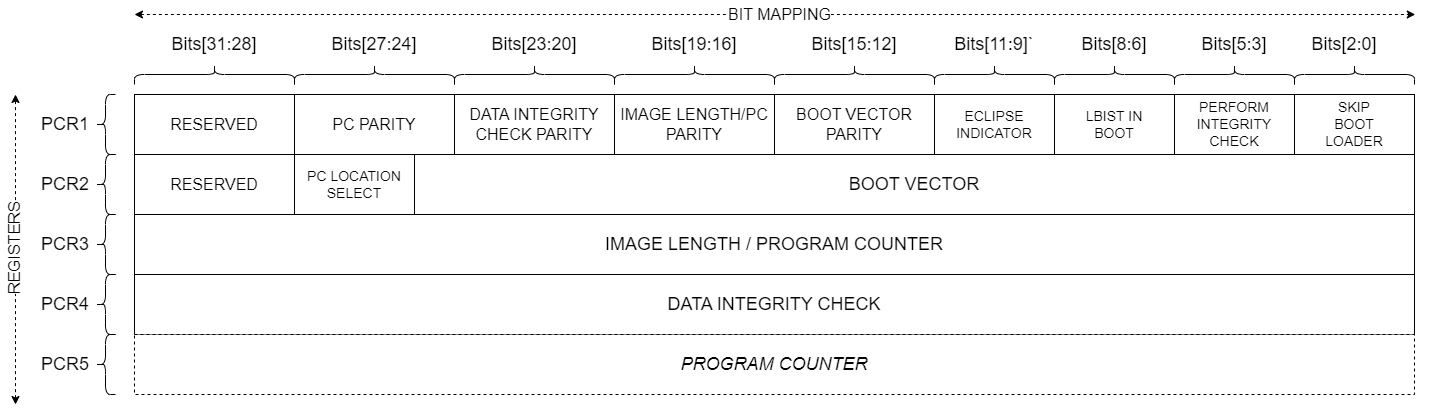

Figure 5-1 shows the organization of relevant PC registers. These registers contain important information that is used by the RBL.

Figure 5-1 Relevant PC Register

Formats

Figure 5-1 Relevant PC Register

Formats