SWRU622A August 2024 – September 2024 AWRL1432 , AWRL6432 , IWRL1432 , IWRL6432 , IWRL6432AOP

- 1

- Trademarks

- 1Introduction

- 2Basic Bootloader Flow

- 3Secondary Bootloader

- 4Warm Reset

- 5Relevant Registers

- 6Revision History

2.6 ROM-Assisted Image Download Sequence

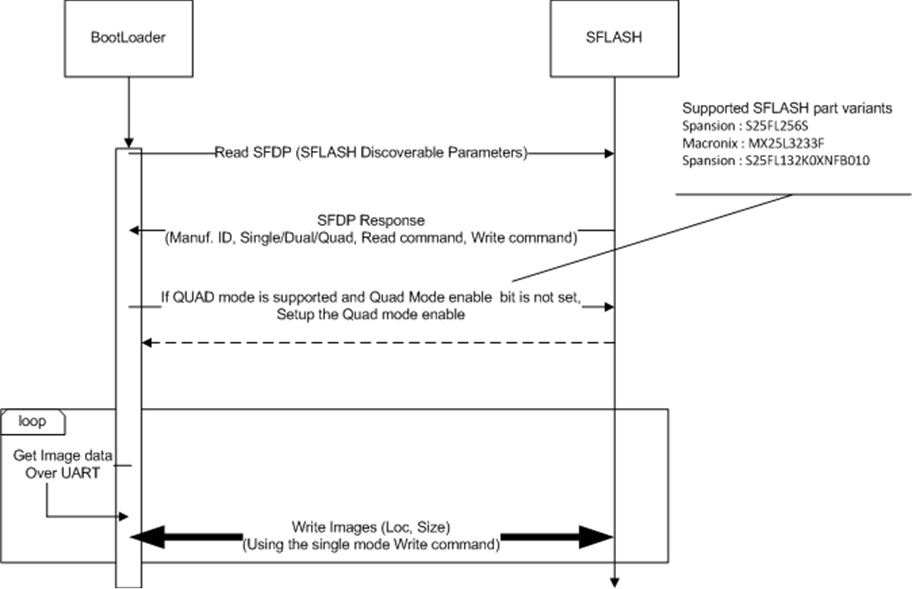

The ROM-assisted image download sequence is entered by placing the device in flashing mode. See Programming Serial Data Flash Over UART (Bootloader Service), for further details on the handshake with an external host to receive the image. Figure 2-2 shows the communication with the serial data flash (SDF).

Figure 2-2 ROM-Assisted Image Download Sequence

Figure 2-2 ROM-Assisted Image Download SequenceKey points:

- The ROM-assisted download should work with all flash variants that allow for memory-mapped mode and Page program command (0x2), with one dummy byte and 24-bit addressing.

- Setting the QE bit varies from one SDF vendor to another. The ROM bootloader supports setting the QE bit for Spansion® and Macronix® variants (certain specific part variants only) in this flow.

- In addition to a checksum-based integrity check for every packet received over the UART, a CRC32-based integrity check is performed over the complete image. The CRC32 is computed incrementally as the packets are received and written to the SDF.