TIDT226 April 2021

4.2 Switch Node

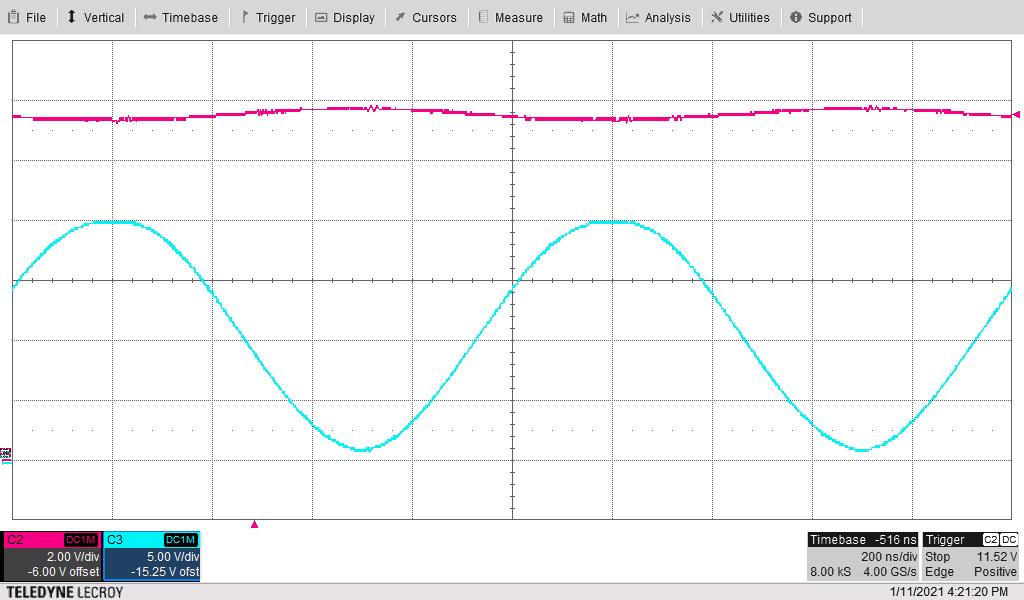

The following waveform shows the primary-side switch node voltage (Red) at TP5 and the total rectified secondary output voltage (Blue). The input voltage is 24 V and the 20-V and –4-V outputs are loaded to 0 mA each.

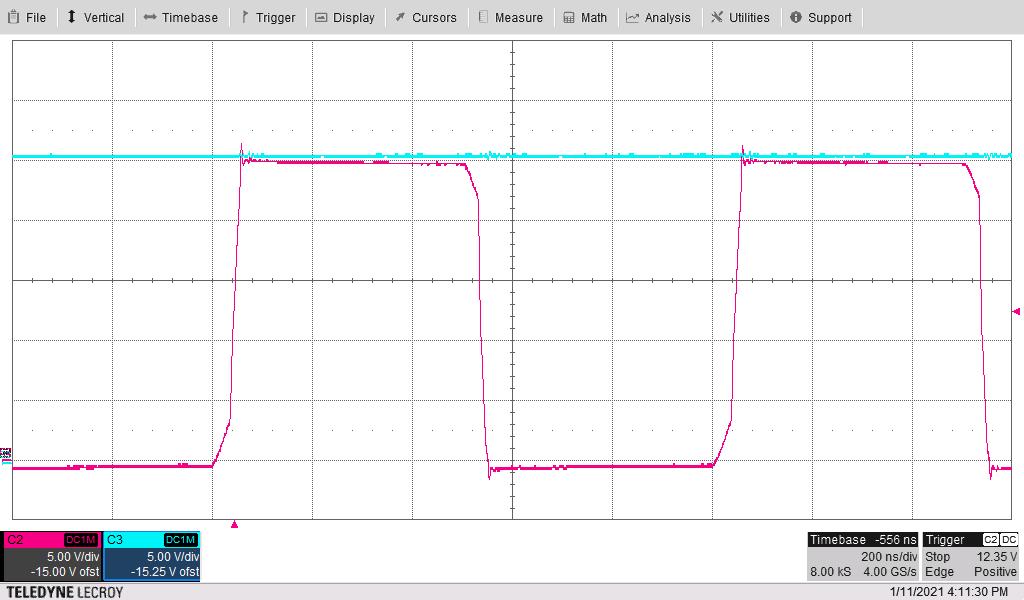

The following waveform shows the primary-side switch node voltage (Red) at TP5 and the total rectified secondary output voltage (Blue). The input voltage is 24 V and the 20-V and –4-V outputs are loaded to 100 mA each.

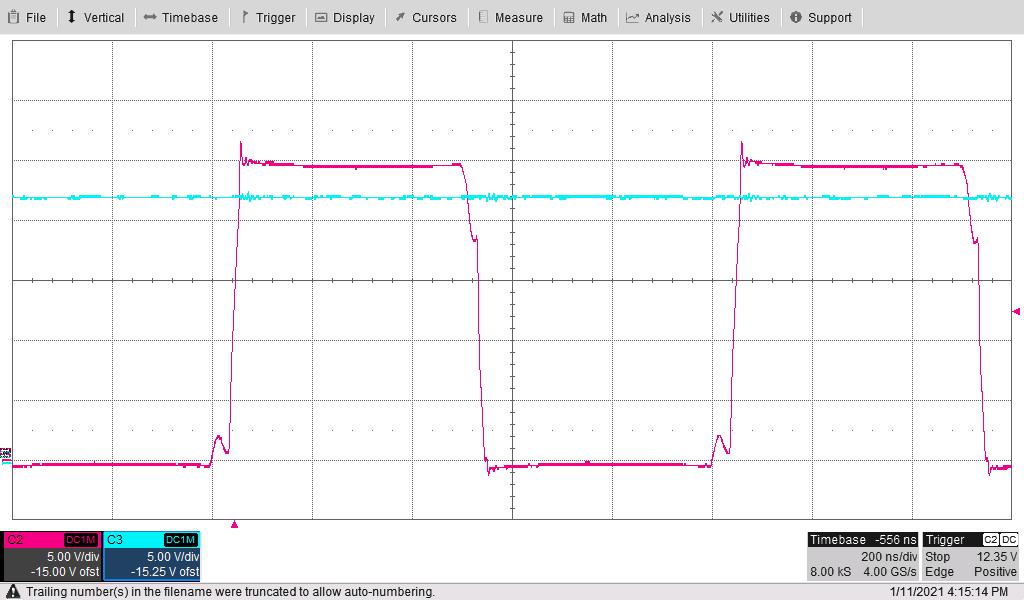

The following waveform shows the primary-side switch node voltage (Red) at TP5 and the total rectified secondary output voltage (Blue). The input voltage is 24 V and the 20-V and –4-V outputs are loaded to 200 mA each.

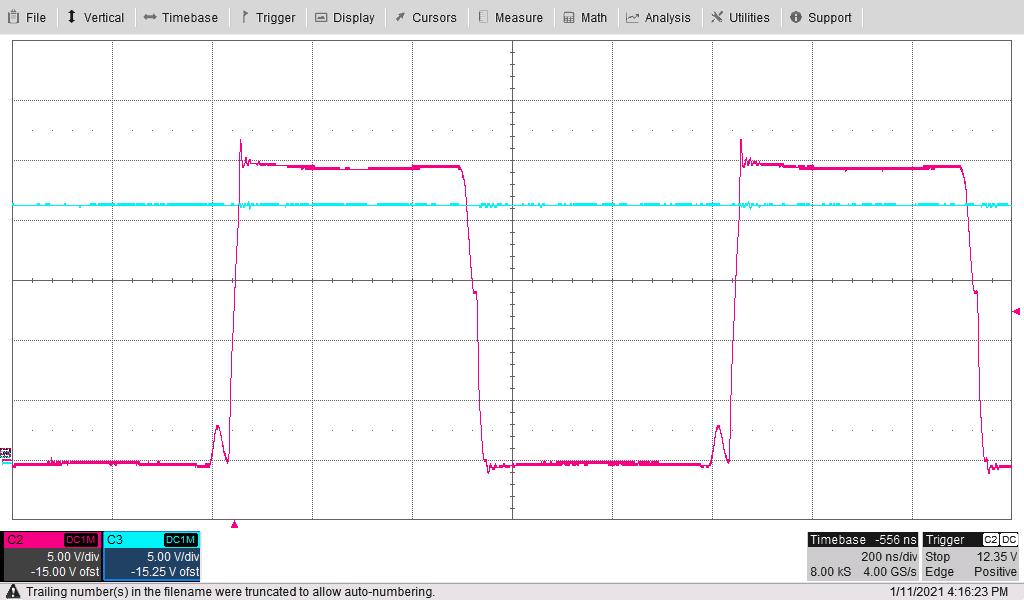

The following waveform shows the primary-side switch node voltage (Red) at TP5 and the total rectified secondary output voltage (Blue). The input voltage is 24 V and the 20-V and –4-V outputs are loaded to 300 mA each.

The following waveform shows the voltage at the middle of the input capacitor divider at C2 and C9 (Red) and the secondary rectified voltage across C3 (Blue). The input voltage is 24 V and the 20-V and –4-V outputs are loaded to 100 mA each.

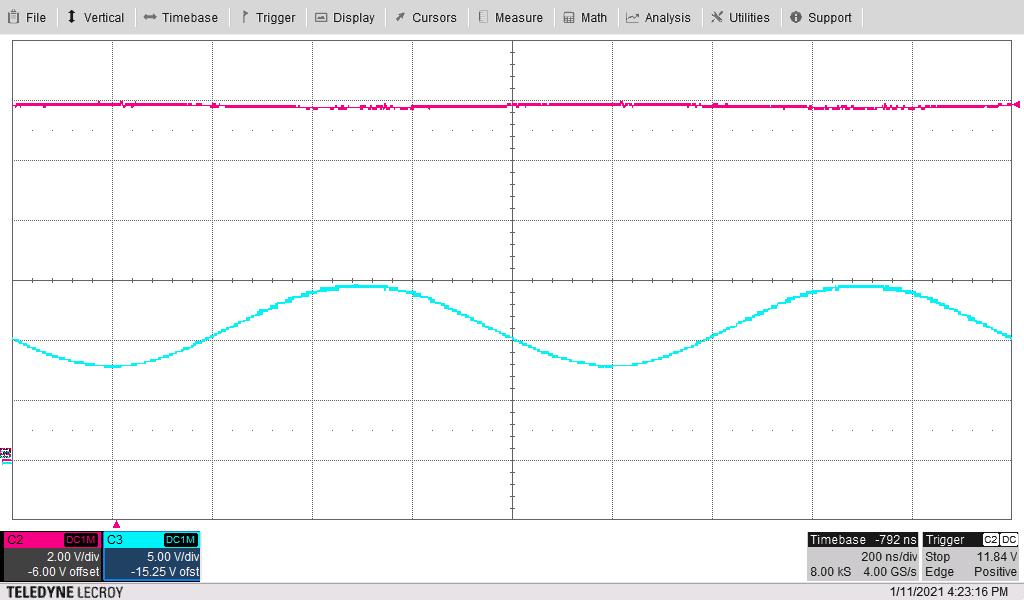

The following waveform shows the voltage at the middle of the input capacitor divider at C2 and C9 (Red) and the secondary rectified voltage across C3 (Blue). The input voltage is 24 V and the 20-V and –4-V outputs are loaded to 300 mA each.