TIDT293 October 2022

5.2 Minimum Voltage

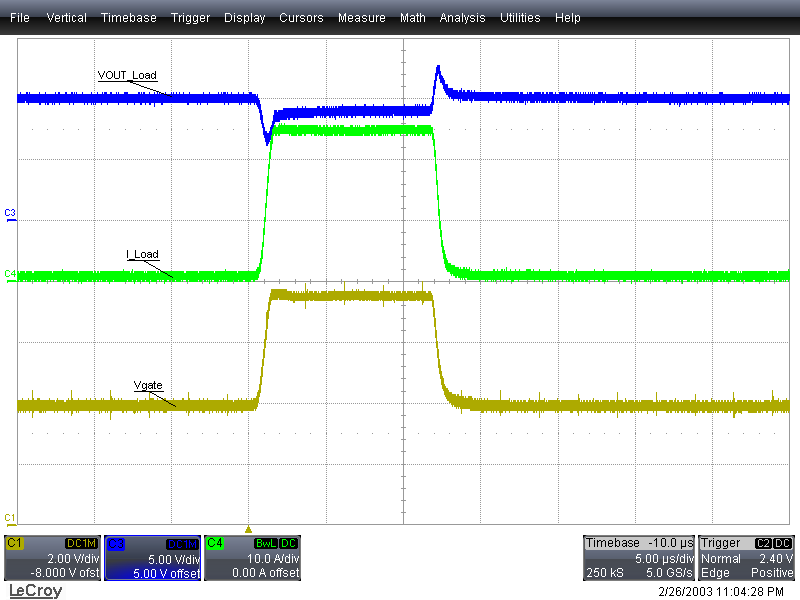

In higher voltage versions, the minimum voltage is limited for the circuit under test due to a higher reference voltage. Testing at a lower output voltage does not allow enough voltage on the FET during the droop. This is also a limitation of the wiring inductance in the setup. Use short wires soldered directly to the load-step board to reduce wiring inductance. The results shown in the following waveform use a PSMN008-75B MOSFET in the 125-A, 50-V variant. The following scope plot is a 1-A to 25-A load transient for a 5-V output exhibiting an abnormal result.

Figure 5-3 1 A to 25 A, 5-V Output Load Transient

Figure 5-3 1 A to 25 A, 5-V Output Load TransientApplying a higher voltage does not collapse the FET voltage and creates a normal load transient. The following scope plot is a 1-A to 25-A load transient with a 10-V output.

Figure 5-4 1-A to 25-A, 10-V Output Load Transient

Figure 5-4 1-A to 25-A, 10-V Output Load Transient