TIDT315 December 2022

- Description

- Features

- Applications

- 1Test Prerequisites

- 2Testing and Results

- 3Waveforms

- A Individual Adjusting of the Rising Edge and Falling Edge With LM5143A

- B Thermal Behavior, Prototype in Vertical Position

- C ON Demand – Assembly of Thermal Interface

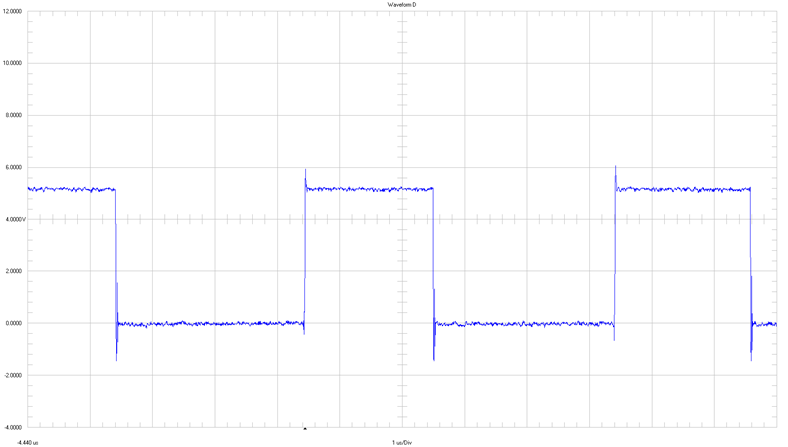

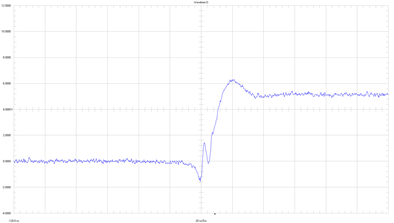

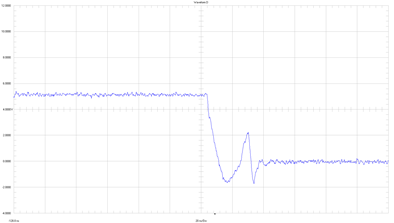

3.1.2.2 Low-Side FET Gate to GND

|

2 V / div 1 µs / div Full bandwidth |

|

|

|

2 V / div 20 ns / div Full bandwidth |

Figure 3-3 Waveform Low-Side FET to

GND