TIDT315 December 2022

- Description

- Features

- Applications

- 1Test Prerequisites

- 2Testing and Results

- 3Waveforms

- A Individual Adjusting of the Rising Edge and Falling Edge With LM5143A

- B Thermal Behavior, Prototype in Vertical Position

- C ON Demand – Assembly of Thermal Interface

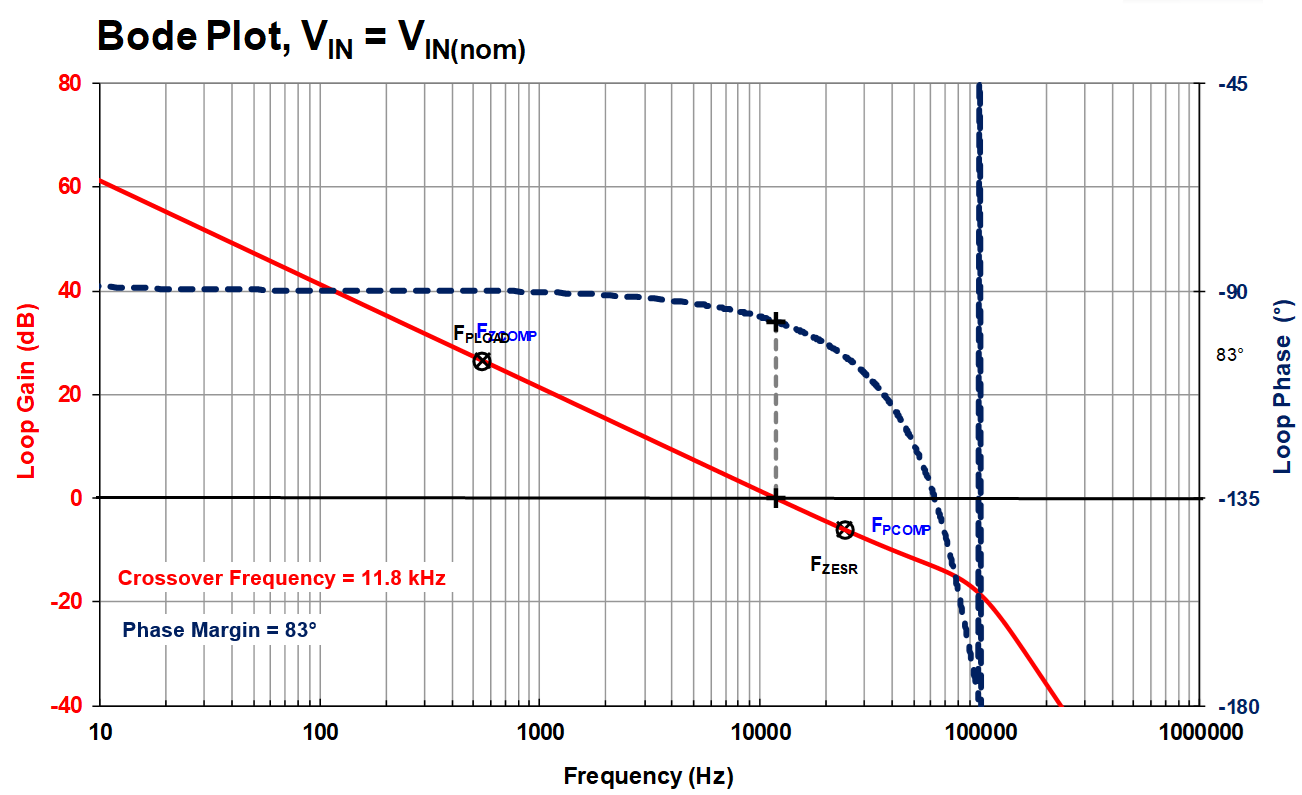

2.4.1 Bode Plot Using Quick Start Design Tool

Figure 2-3 Bode Plot Derived From the

Quick Start Design Tool

Figure 2-3 Bode Plot Derived From the

Quick Start Design ToolDownload the quick start design tool from LM5143DESIGN-CALC.

Figure 2-3 is calculated for gain resistor 19.6 kΩ, zero capacitor 15 nF, and a pole capacitor of 330 pF at the error amplifier.

Figure 2-4 shows the matching measurement with VIN = 24 V and IOUT = 50 A.