TIDT316 December 2022

- Description

- Features

- Applications

- 1Test Prerequisites

- 2Testing and Results

- 3Waveforms

- A Output Ripple Reduction, Output Current Capability, and Dithering Option

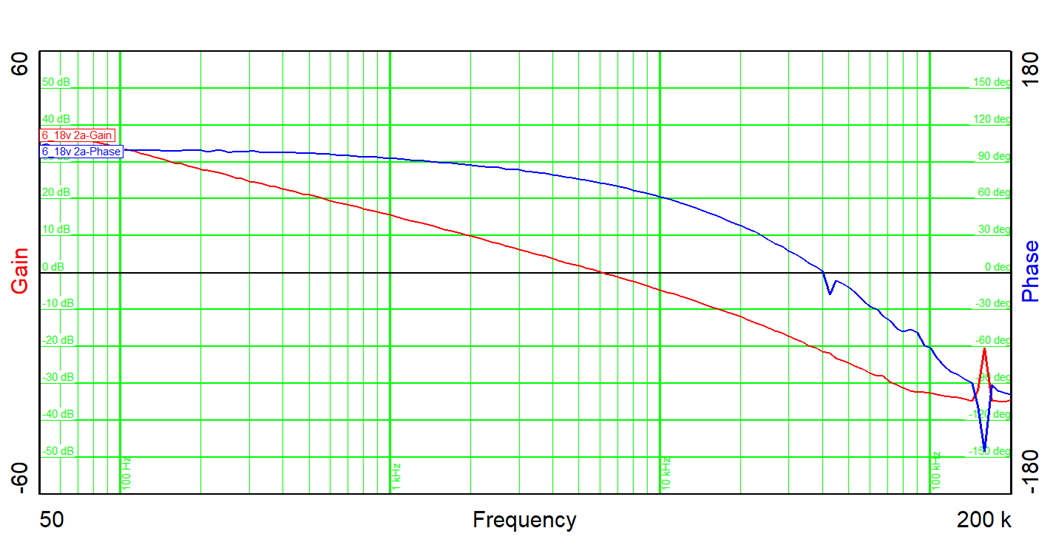

2.6.3 18-V Input Voltage

Figure 2-8 Bode Plot for 18-V Input

Voltage and 2-A Output Current

Figure 2-8 Bode Plot for 18-V Input

Voltage and 2-A Output Current