TIDT328 april 2023

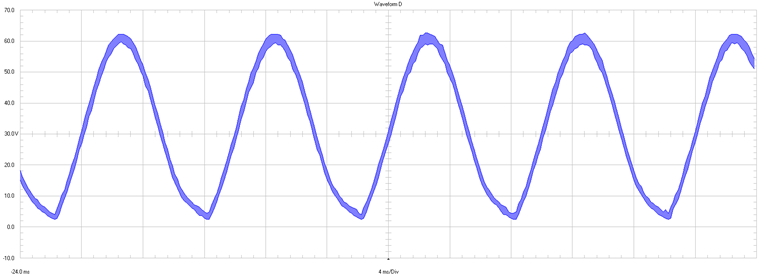

A.1.3.2 Sinus 100 Hz

|

10 V / div 4 ms / div full bandwidth |

Figure 4-4 Modulation Sinus (5

VPP + 2.5 V) 100 Hz, 12 VIN, 200-Ω Load

Note: The hardware shows the nonlinearity at Fmod 100

Hz similar to simulation.