TIDT336 may 2023

3.5 Shutdown Sequence

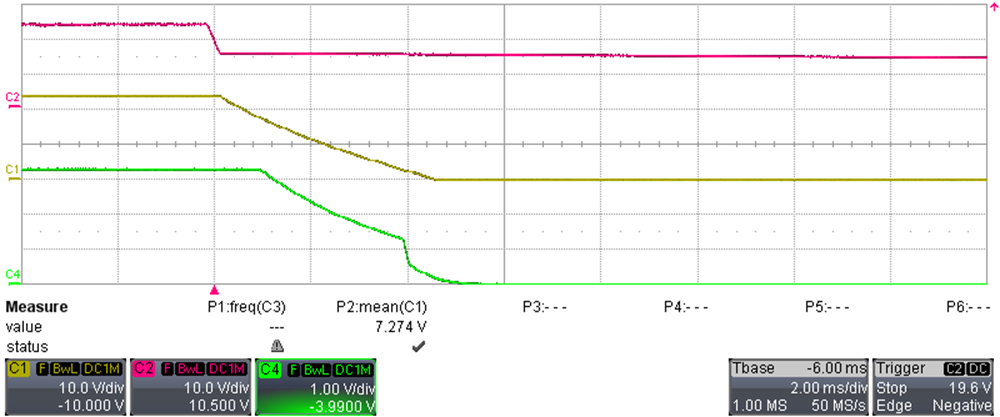

The shutdown phase of the converter was analyzed by supplying the circuit with 24 VDC but only at full-load condition. All waveforms were taken at 20-MHz bandwidth limit and DC coupling.

|

C2: VIN (10 V / div) C1: 24 VOUT (10 V / div) C4: 3.3 VOUT (1 V / div) (2 ms / div) |

Figure 3-9 Shutdown with Full Load (at both Outputs)