TIDT336 may 2023

3.2 Output Voltage Ripple

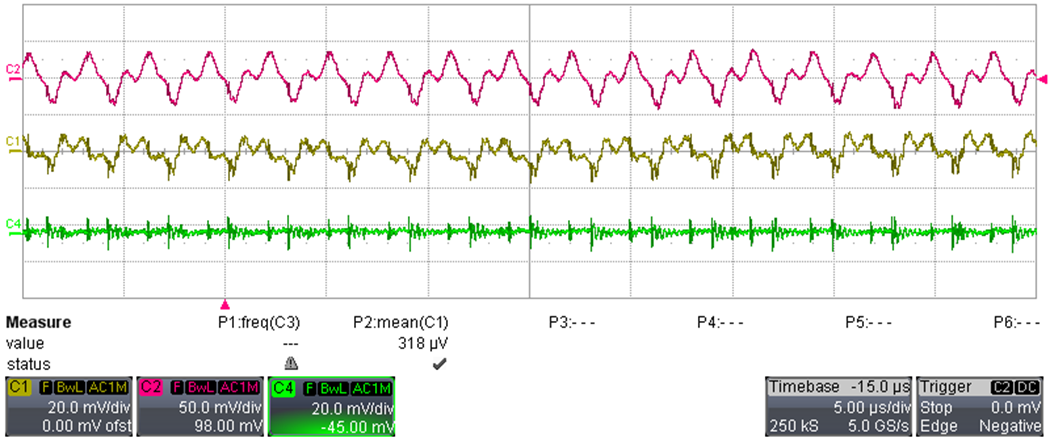

The 3.3-V and 24-V outputs, as well as input voltage and ripple were measured by supplying the converter at 24 VDC with both outputs loaded at nominal current. The bandwidth limit of the scope was set to 20 MHz, and the coupling to AC.

|

C1: 24 VOUT (20 mV / div) C2: VIN (50 mV / div) C4: 3.3 VOUT (20 mV / div) (5 µs / div) |

Figure 3-4 Output Voltage

Ripple With 5 µs / div

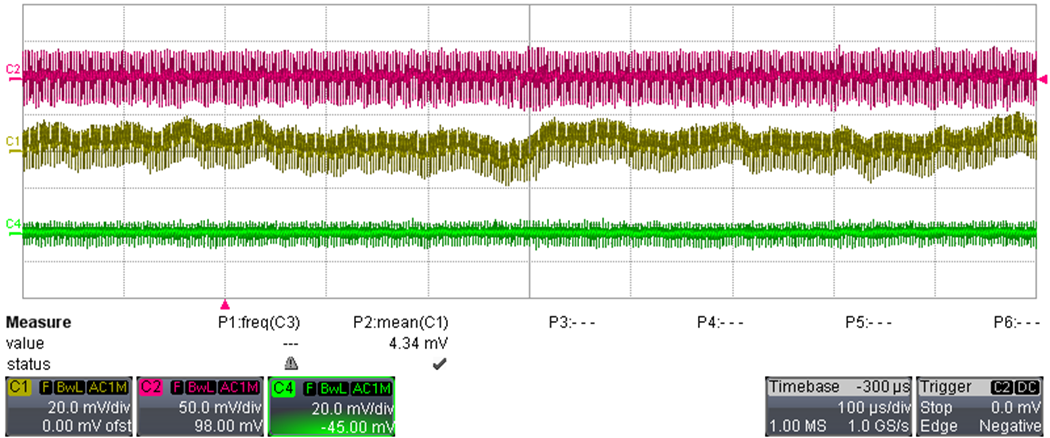

Figure 3-5 is the same waveform as in Figure 3-10 but with longer time division for showing details about low-frequency ripple.

|

C1: 24 VOUT (20 mV / div) C2: VIN (50 mV / div) C4: 3.3 VOUT (20 mV / div) (100 µs / div) |

Figure 3-5 Output Voltage

Ripple With 100 µs / div