TIDT357 November 2023

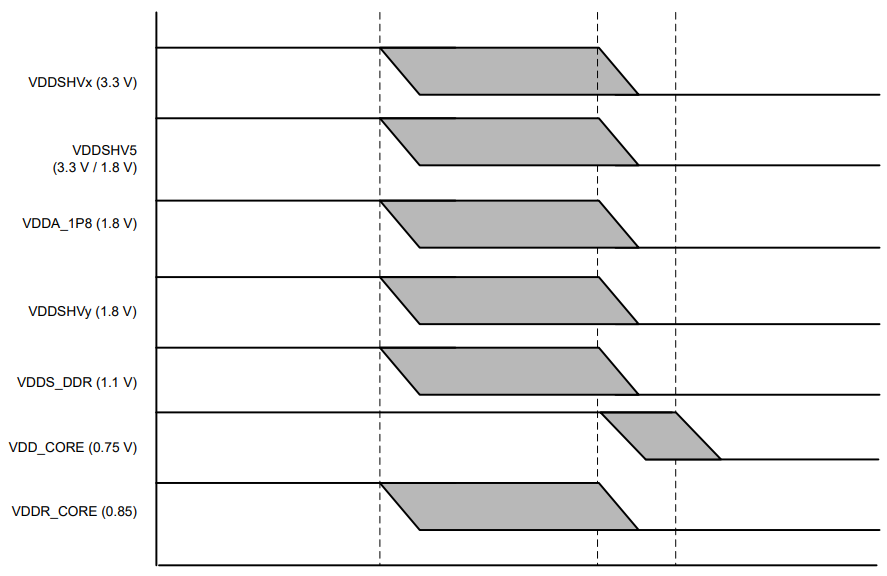

1.2 Power-Off Sequence

As described in the power-down sequencing section of the AM62Ax Sitara™ Processors data sheet, all power rails except VDD_CORE and VDDR_CORE can be ramped down independent of each other. If VDD_CORE is operating at 0.75 V, ramp down VDD_CORE after the 0.85 V VDDR_CORE. For the case where VDD_CORE and VDDR_CORE both run from a common 0.85-V supply, there is no ramp down requirement between them.

Figure 1-3 AM62x-Q1 Power-Off Sequence

Figure 1-3 AM62x-Q1 Power-Off Sequence