TIDUAY6E November 2015 – March 2020

3.2.3 Control Scheme

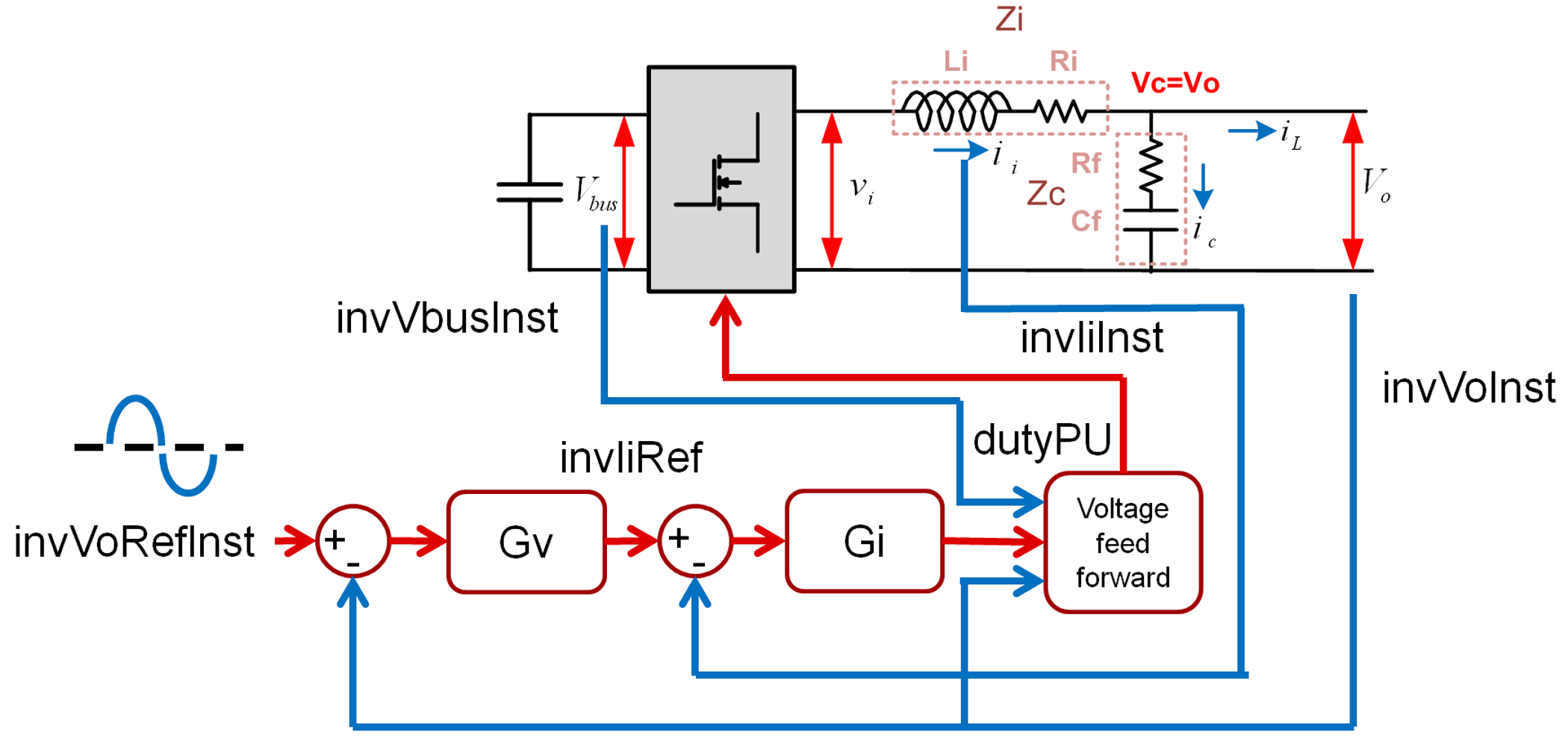

Figure 12 shows a cascaded control loop scheme, which controls the output voltage of the inverter. Input DC bus voltage Vbus, inductor current ii, and output voltage Vo are sensed by the MCU.

Figure 12. Control Scheme Used for Output Voltage Control

Figure 12. Control Scheme Used for Output Voltage Control First, a reference sinusoidal value invVoRefInst is generated. This value is compared with the sensed output voltage invVoInst and the error fed into the voltage compensator Gv. In case of AC voltage control, the tracking error needs to be zeroed for the AC frequency; hence, a proportional resonant controller is used in Gv to zero the fundamental voltage error.

NOTE

A proportional integral controller zeroes error at DC and is not able to eliminate steady state error when the reference is a sinusoidal signal.

Additional resonant controllers are added to the voltage compensator to zero the error at harmonic frequency of the fundamental frequency being generated. A lead lag compensator is also added to the voltage compensator to improve the phase margin in the reference design.

Where N is the total number of harmonic compensators added in the voltage control loop. A total of four compensators that compensate the first harmonic, third harmonic, fifth harmonic, and seventh harmonic are used in this reference design. The compensation designer models the voltage loop plant and enables tuning of the voltage loop compensator coefficients through the powerSUITE CFG page.

Figure 13 shows the control model used to model the voltage source inverter operation.

The design of the voltage loop is aided by an inner current loop. The voltage compensator generates a current reference (invIiRefInst) for the current loop in which a current compensator Gi is used. Both DC bus voltage and output voltage feedforward in the current loop make the plant simple, and the PI controller can be used to tune the current compensator. The plant model of the inverter current loop is available inside compensation designer, which can be invoked from the powerSUITE page.