TIDUD61E October 2020 – April 2021

- Description

- Resources

- Features

- Applications

- 5

- 1System Description

- 2System Overview

-

3Hardware, Software, Testing Requirements, and Test Results

- 3.1

Required Hardware and Software

- 3.1.1 Hardware

- 3.1.2

Software

- 3.1.2.1 Opening Project Inside CCS

- 3.1.2.2 Project Structure

- 3.1.2.3 Using CLA on C2000 MCU to Alleviate CPU Burden

- 3.1.2.4 CPU and CLA Utilization and Memory Allocation

- 3.1.2.5

Running the Project

- 3.1.2.5.1 Lab 1: Open Loop, DC (PFC Mode)

- 3.1.2.5.2 Lab 2: Closed Current Loop DC (PFC)

- 3.1.2.5.3 Lab 3: Closed Current Loop, AC (PFC)

- 3.1.2.5.4 Lab 4: Closed Voltage and Current Loop (PFC)

- 3.1.2.5.5 Lab 5: Open loop, DC (Inverter)

- 3.1.2.5.6 Lab 6: Open loop, AC (Inverter)

- 3.1.2.5.7 Lab 7: Closed Current Loop, DC (Inverter with resistive load)

- 3.1.2.5.8 Lab 8: Closed Current Loop, AC (Inverter with resistive load)

- 3.1.2.5.9 Lab 9: Closed Current Loop (Grid Connected Inverter)

- 3.1.2.6 Running Code on CLA

- 3.1.2.7

Advanced Options

- 3.1.2.7.1 Input Cap Compensation for PF Improvement Under Light Load

- 3.1.2.7.2 83

- 3.1.2.7.3 Adaptive Dead Time for Efficiency Improvements

- 3.1.2.7.4 Phase Shedding for Efficiency Improvements

- 3.1.2.7.5 Non-Linear Voltage Loop for Transient Reduction

- 3.1.2.7.6 Software Phase Locked Loop Methods: SOGI - FLL

- 3.2 Testing and Results

- 3.1

Required Hardware and Software

- 4Design Files

- 5Software Files

- 6Related Documentation

- 7About the Author

- 8Revision History

3.1.2.5.9.2 Building and Loading Project and Setting up Debug

- Right click on the project name, and click Rebuild Project. The project builds successfully. Click Run → Debug, which launches a debugging session. In the case of dual CPU devices, a window may appear to select the CPU the debug must be performed. In this case, select CPU1. The project then loads on the device, and CCS debug view becomes active. The code halts at the start of the main routine.

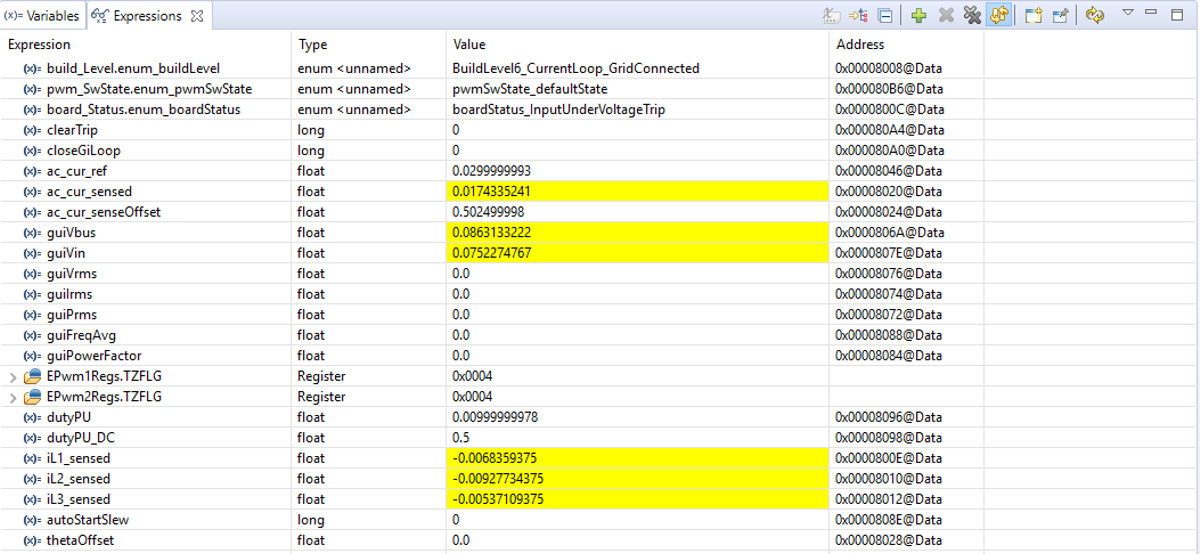

- To add the variables in the watch and expressions window click View → Scripting Console to open the scripting console dialog box. On the upper right corner of this console, click on Open to browse to the setupdebugenv_lab9.js script file, which is located inside the project folder. This file populates the watch window with appropriate variables required to debug the system. Click on Continuous Refresh button (

) on the watch window to enable continuous update of values from the controller. The watch window appears as Figure 3-35.

) on the watch window to enable continuous update of values from the controller. The watch window appears as Figure 3-35.

Figure 3-39 Lab 9: Closed Current Loop (Grid-connected) Expressions View

Figure 3-39 Lab 9: Closed Current Loop (Grid-connected) Expressions View - Enable real-time mode by hovering the mouse on the buttons on the horizontal toolbar, and clicking the

button.

button. - Run the project by clicking on

- Now Halt the processor by using the Halt button on the toolbar (