TIDUDT0 September 2022

3.3.2.3 TPSM5D1806 Transient Results

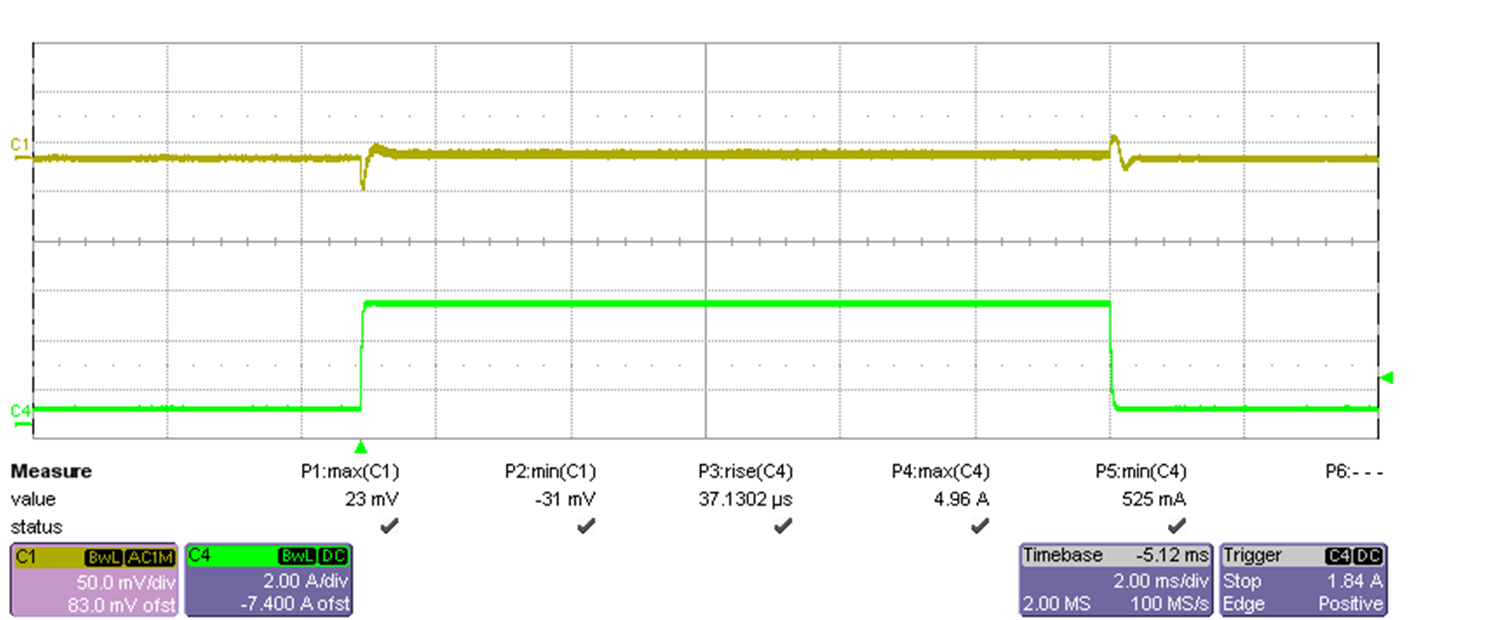

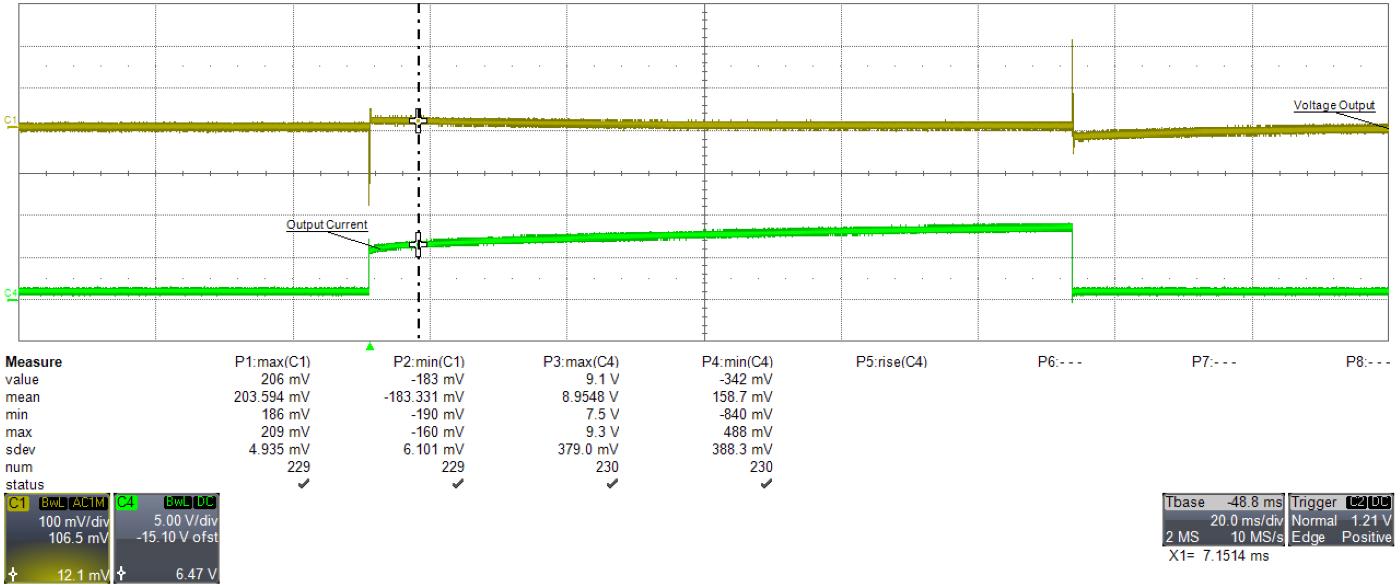

Figure 3-22 TPSM5D1806 Transient 0.9 V, 6

A

Figure 3-22 TPSM5D1806 Transient 0.9 V, 6

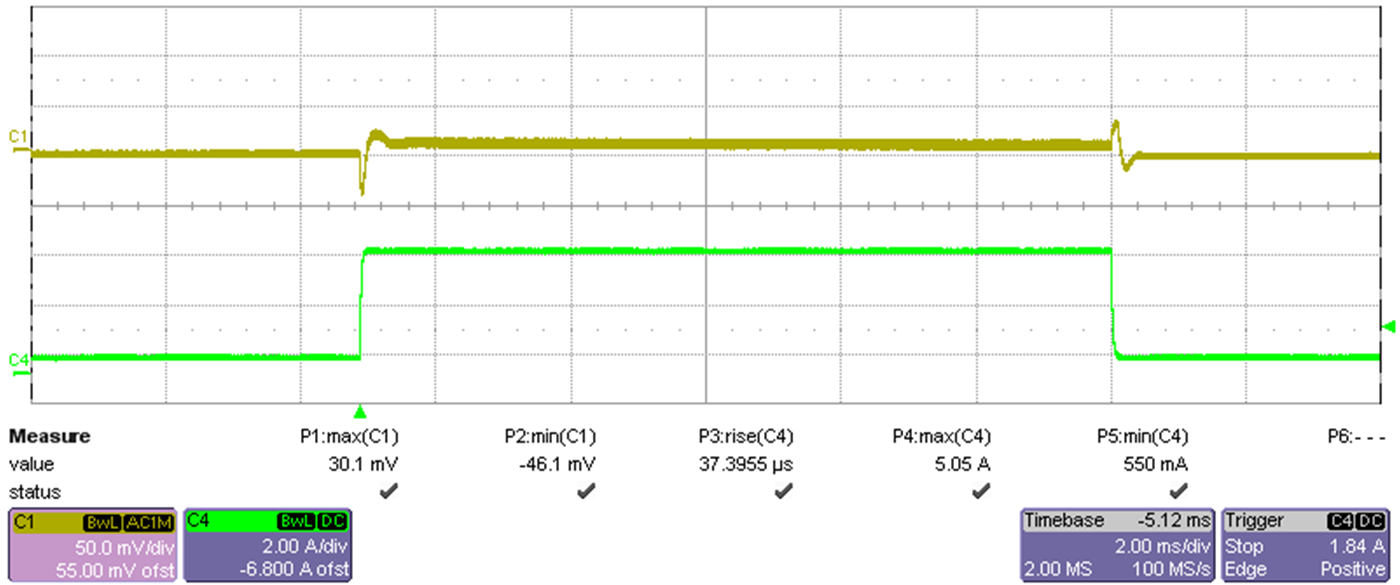

A Figure 3-23 TPSM5D1806 Transient 1.2 V, 6

A

Figure 3-23 TPSM5D1806 Transient 1.2 V, 6

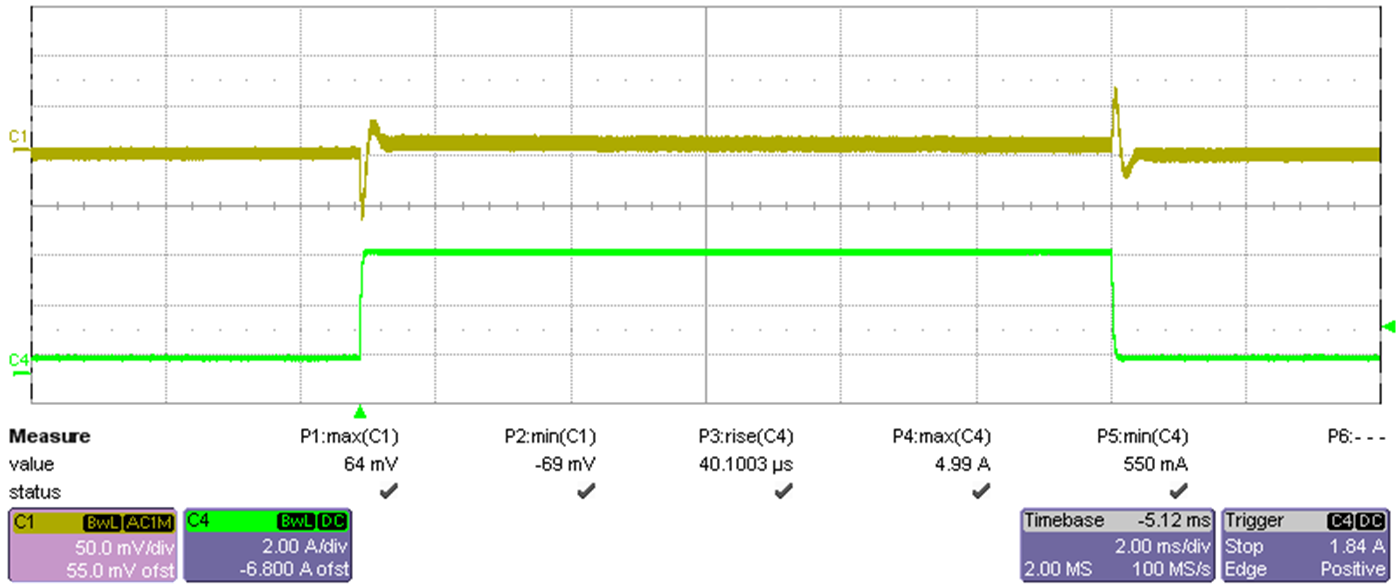

A Figure 3-24 TPSM5D1806 Transient 1.8 V, 6

A

Figure 3-24 TPSM5D1806 Transient 1.8 V, 6

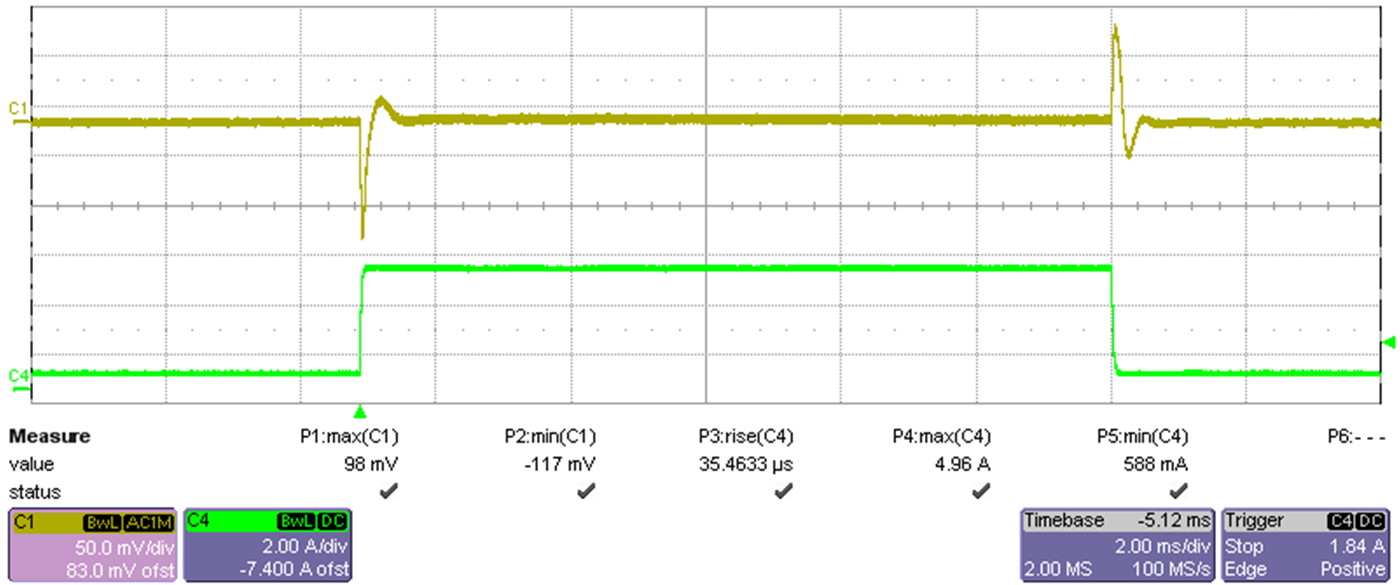

A Figure 3-25 TPSM5D1806 Transient 3.3 V, 5

A

Figure 3-25 TPSM5D1806 Transient 3.3 V, 5

A Figure 3-26 TPSM5D1806 Transient 5 V, 10

A

Figure 3-26 TPSM5D1806 Transient 5 V, 10

A