TIDUDT0 September 2022

3.3.2.2 TPS650861 Transient Results

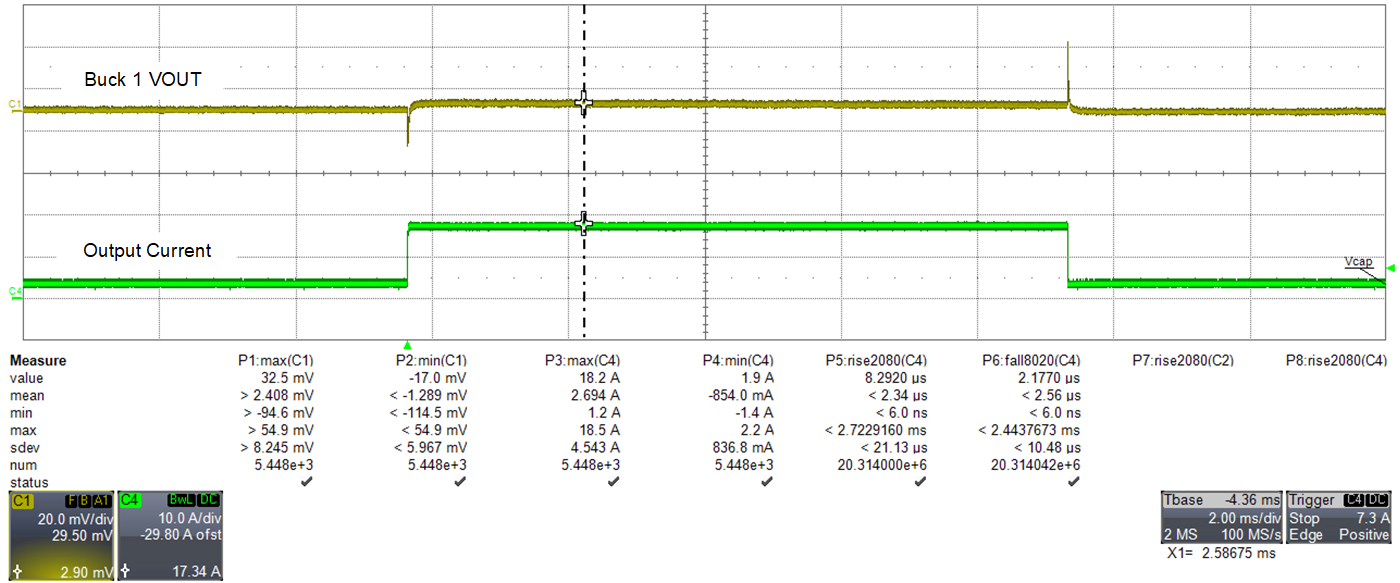

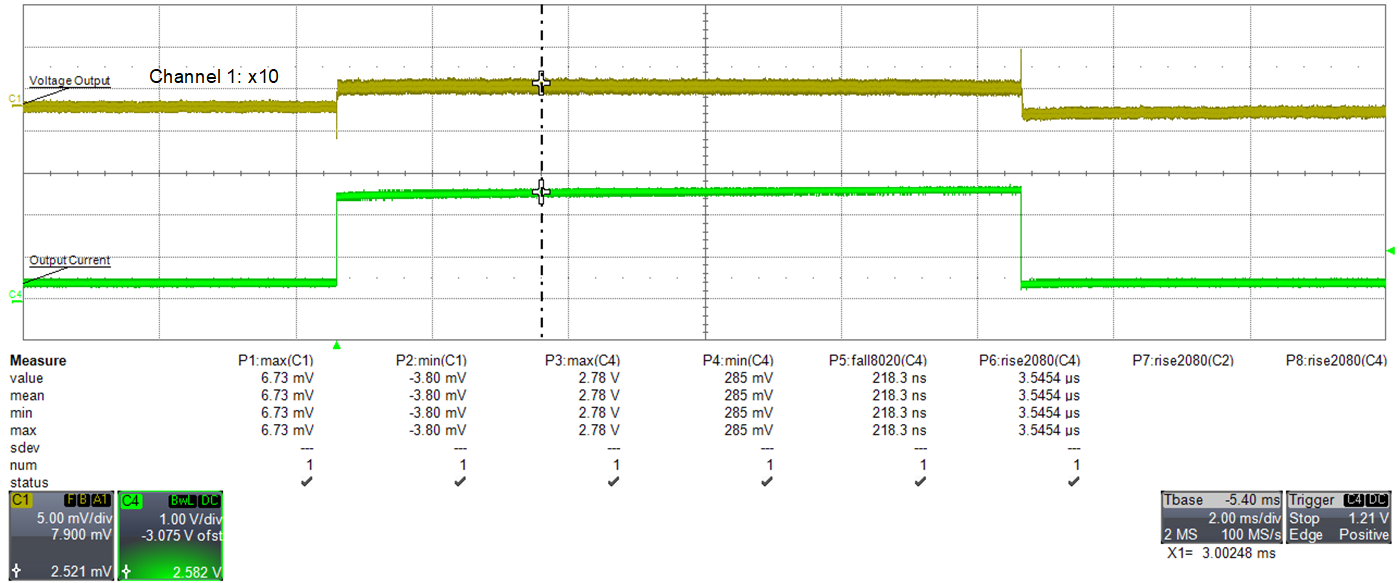

Figure 3-16 TPS650861 Buck 1 Transient 0.9

V, 20 A

Figure 3-16 TPS650861 Buck 1 Transient 0.9

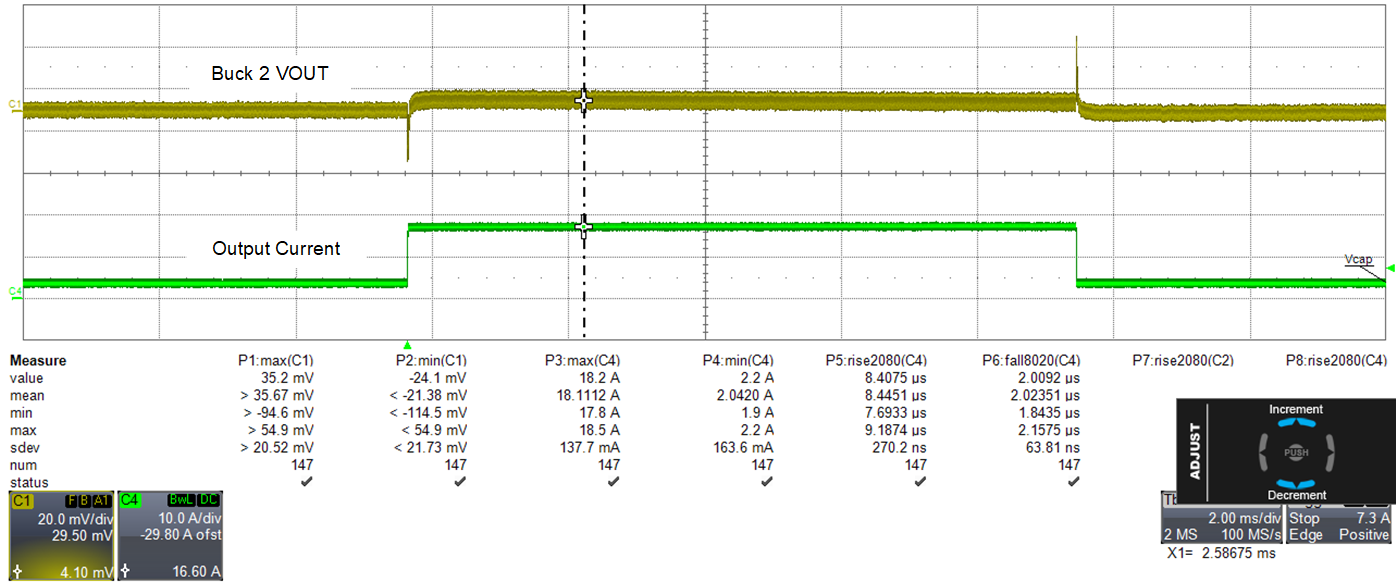

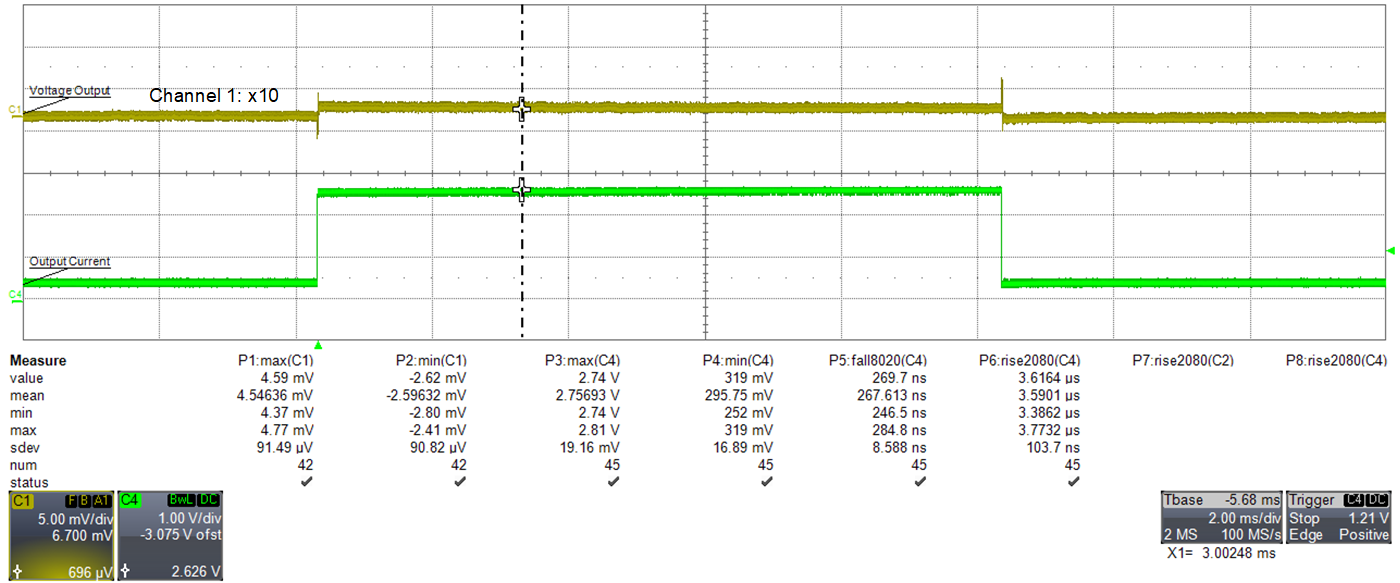

V, 20 A Figure 3-17 TPS650861 Buck 2 Transient 1.8

V, 20 A

Figure 3-17 TPS650861 Buck 2 Transient 1.8

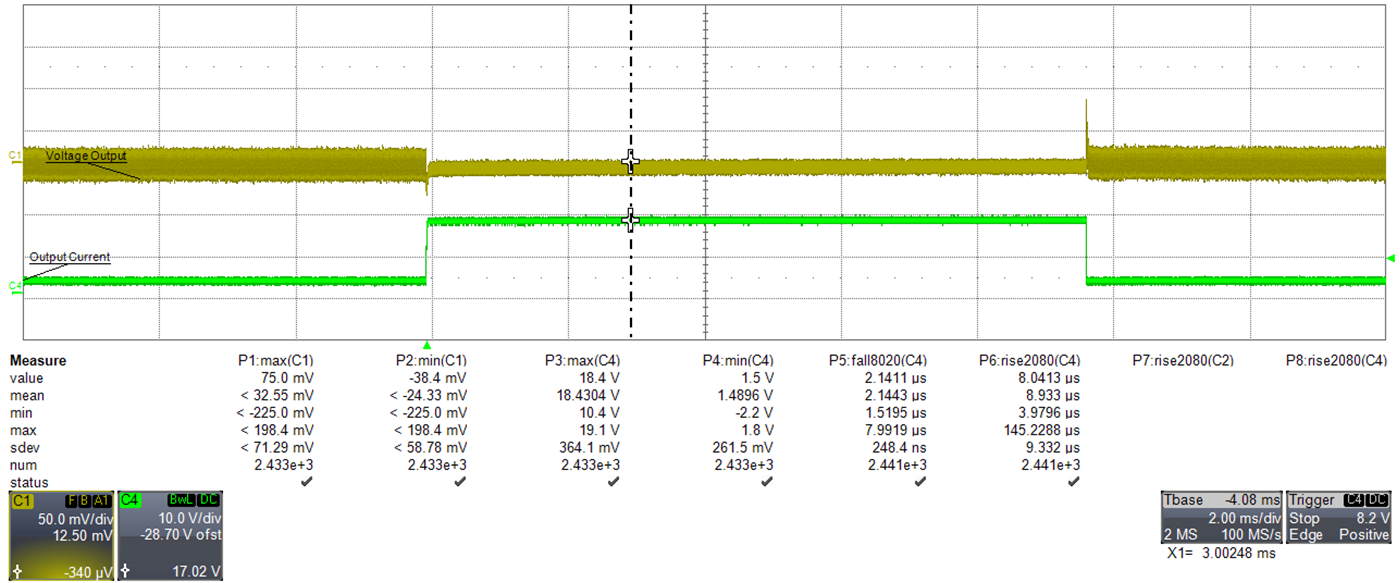

V, 20 A Figure 3-18 TPS650861 Buck 6 Transient 1.2

V, 20 A

Figure 3-18 TPS650861 Buck 6 Transient 1.2

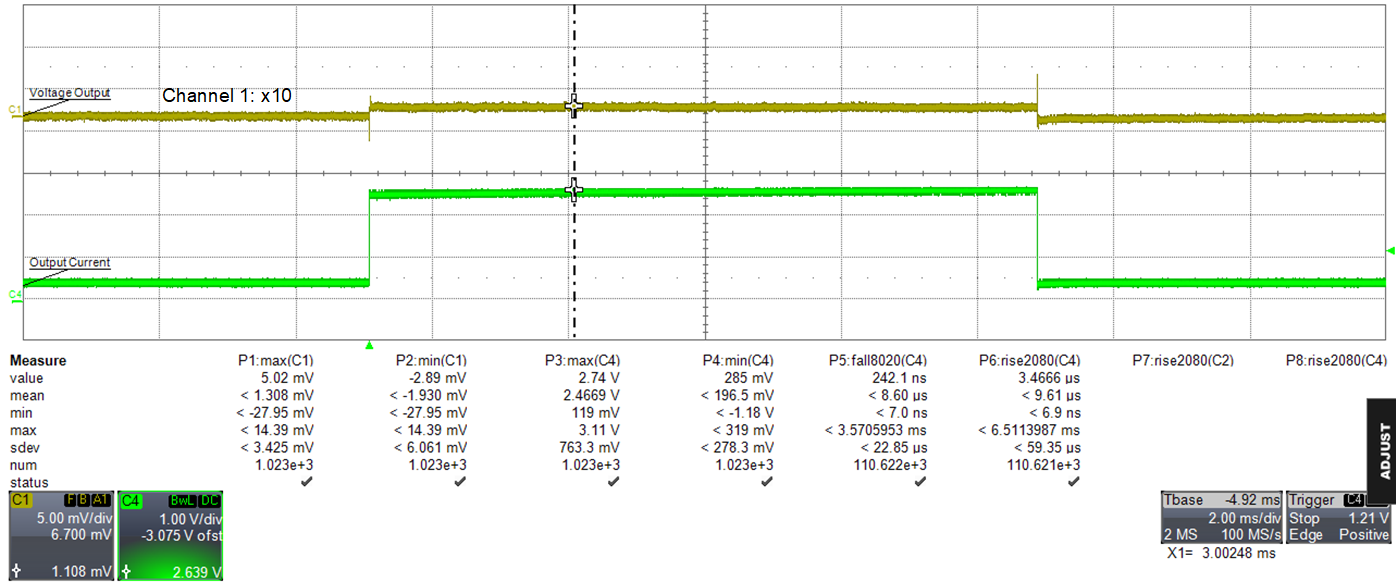

V, 20 A Figure 3-19 TPS650861 Buck 3 Transient 1.8

V, 3 A

Figure 3-19 TPS650861 Buck 3 Transient 1.8

V, 3 A Figure 3-20 TPS650861 Buck 4 Transient 2.5

V, 3 A

Figure 3-20 TPS650861 Buck 4 Transient 2.5

V, 3 A Figure 3-21 TPS650861 Buck 5 Transient 1.2

V, 3 A

Figure 3-21 TPS650861 Buck 5 Transient 1.2

V, 3 A