TIDUEY8 March 2023

- Description

- Resources

- Features

- Applications

- 5

- 1System Description

-

2System Overview

- 2.1 Design Block Diagram

- 2.2 Highlighted Products

- 2.3

Design Steps

- 2.3.1 Multiple JESD204B Synchronization Requirements

- 2.3.2 Clock Tree Design

- 2.3.3 Power Management

- 3Getting Started Hardware and Software

- 4Testing and Results

- 5Design and Documentation Support

- 6About the Authors

2.3.2.4 Phase-Noise Optimization

Analog signal chain performance depends on the phase noise and jitter performance of the clock, which can affect the SNR, ENOB, and SFDR, of the data converter. Therefore, optimize the phase noise of the clock to having the lowest jitter.

The LMX2615-SP optimized-loop filter can be programmed to minimize phase noise with the PLLatinum™ simulation tool. In this design, the loop filter are kept the same as LMX2615-SP EVM components.

| PARAMETER | VALUE |

|---|---|

| VCO Gain | 132 MHz/V |

Loop Bandwidth | 285 kHz |

Phase Margin | 65 deg |

C1_LF | 390 nF |

C2_LF | 68 nF |

C3_LF | Open |

C4_LF | 1.8 nF |

R2 | 68 Ω |

R3_LF | 0 Ω |

R4_LF | 18 Ω |

Charge Pump Gain | 15 mA |

Phase Detector Frequency | 200 MHz |

VCO Frequency | Designed for 15 GHz, but works over the whole frequency range |

The ADC SNR degrades due to external clock jitter and internal ADC aperture jitter. SNR of the ADC, limited by the total jitter, is calculated as:

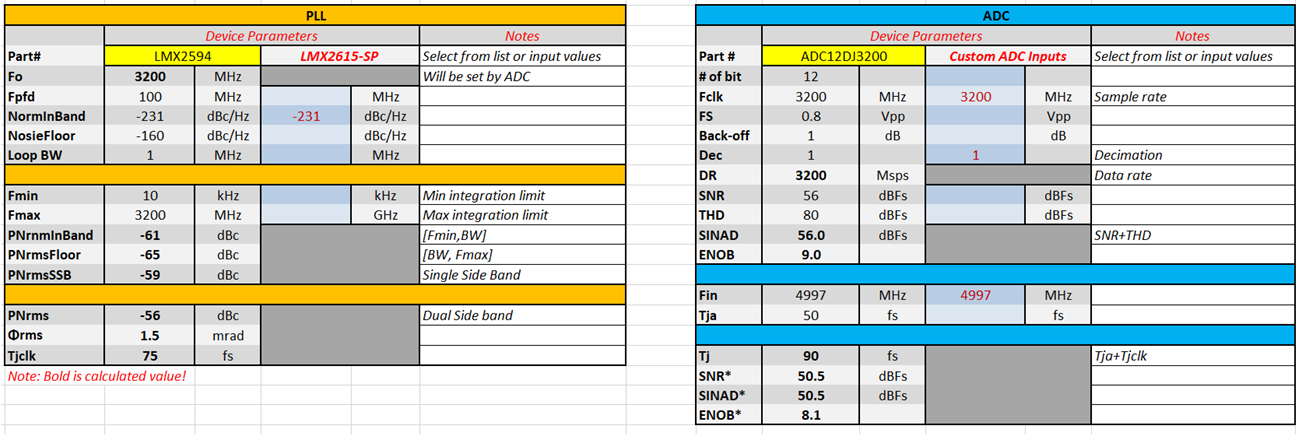

To calculate the SNR performance of the ADC12DJ3200-SP over the clocking performance, TI provides a tool with the Jitter and SNR Calculator for ADCs (JITTER-SNR-CALC). Figure 2-7 is a screen-shot with the calculation results:

Figure 2-7 Screen-Shot Jitter to SNR Tool

Figure 2-7 Screen-Shot Jitter to SNR ToolFigure 2-8 and Figure 2-9 show the relevant SNR plots.

Figure 2-8 SNR vs TJ

Figure 2-9 SNR vs FIN