TIDUEY8 March 2023

- Description

- Resources

- Features

- Applications

- 5

- 1System Description

-

2System Overview

- 2.1 Design Block Diagram

- 2.2 Highlighted Products

- 2.3

Design Steps

- 2.3.1 Multiple JESD204B Synchronization Requirements

- 2.3.2 Clock Tree Design

- 2.3.3 Power Management

- 3Getting Started Hardware and Software

- 4Testing and Results

- 5Design and Documentation Support

- 6About the Authors

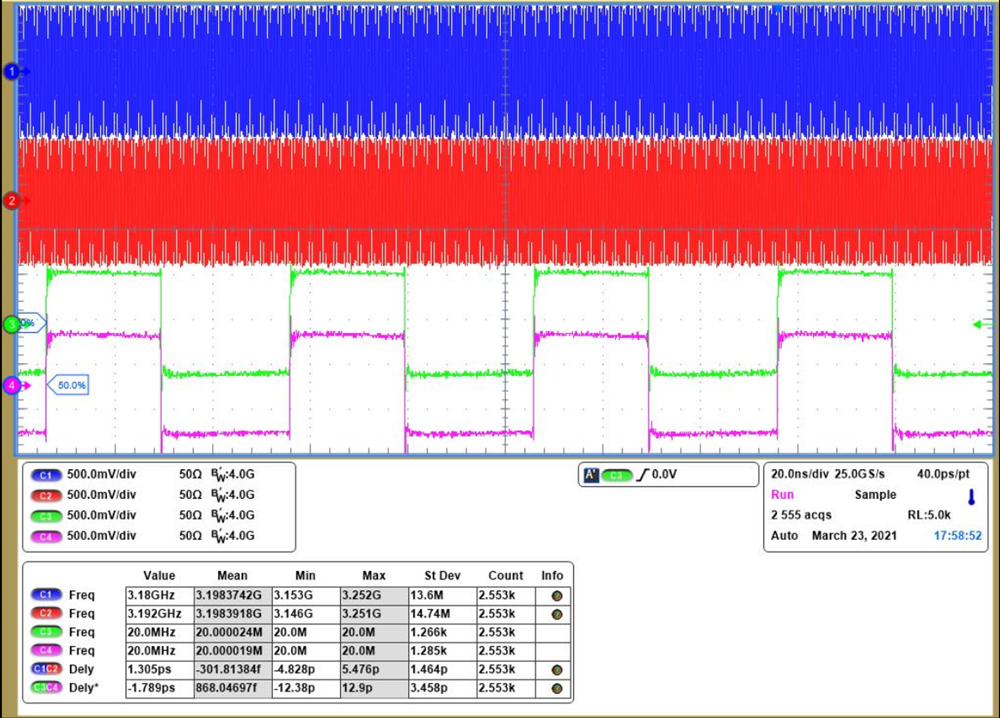

4.2.2 Multichannel Clock Phase Alignment

As explained in Section 3.2.3, synchronized clocks are critical for multichannel systems. This section shows the measured phase aligned clocks and SYSREFs that are generated from both LMX2615-SP devices at a 3.2-GHz device clock and 20-MHz SYSREF. The minimum skew have between the clocks, reflects the minimum channel-to-channel skew in multichannel systems. In this test, the TIDA-010191 clock board shows the clock skew less than 5 ps. As a result, can reduce the channel-to-channel skew in multichannel systems. Figure 4-8 shows the multichannel clock skew measured results from two LMX2615-SP devices at the device clocks and SYSREF signals.

Figure 4-8 Scope-Shot Multichannel Clock

Phase Alignment

Figure 4-8 Scope-Shot Multichannel Clock

Phase Alignment