TIDUEY8 March 2023

- Description

- Resources

- Features

- Applications

- 5

- 1System Description

-

2System Overview

- 2.1 Design Block Diagram

- 2.2 Highlighted Products

- 2.3

Design Steps

- 2.3.1 Multiple JESD204B Synchronization Requirements

- 2.3.2 Clock Tree Design

- 2.3.3 Power Management

- 3Getting Started Hardware and Software

- 4Testing and Results

- 5Design and Documentation Support

- 6About the Authors

4.2.3 Signal Chain Performance

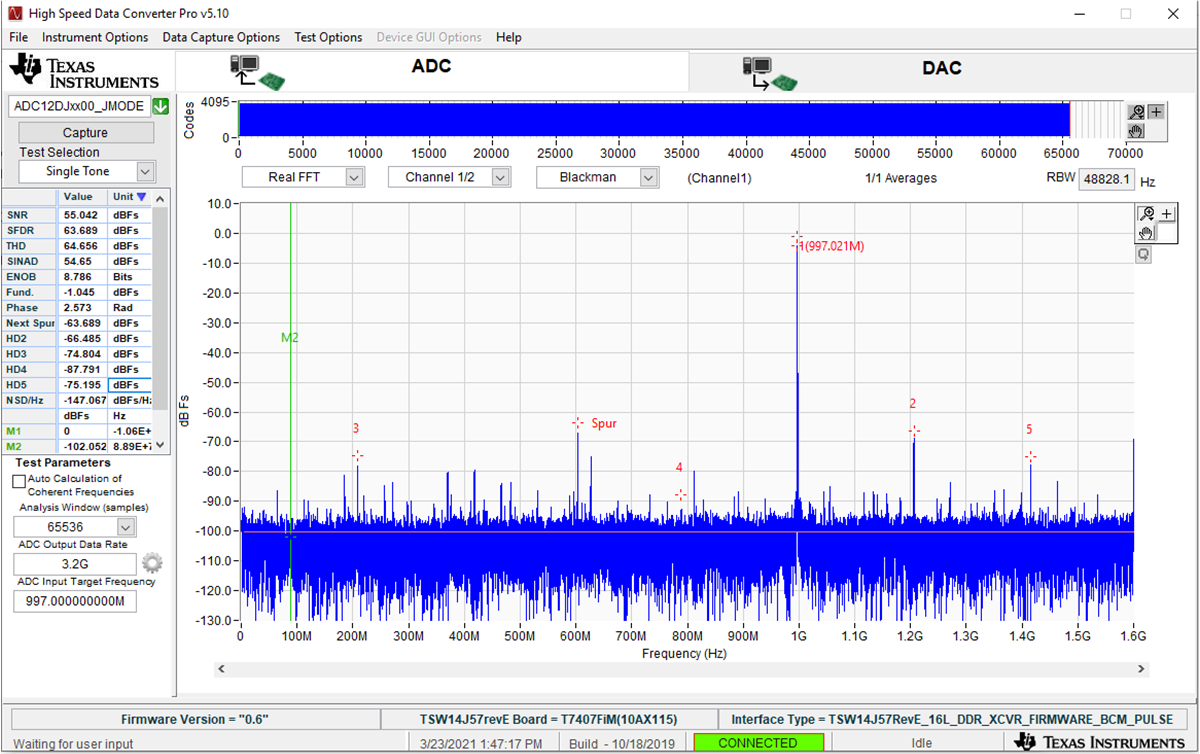

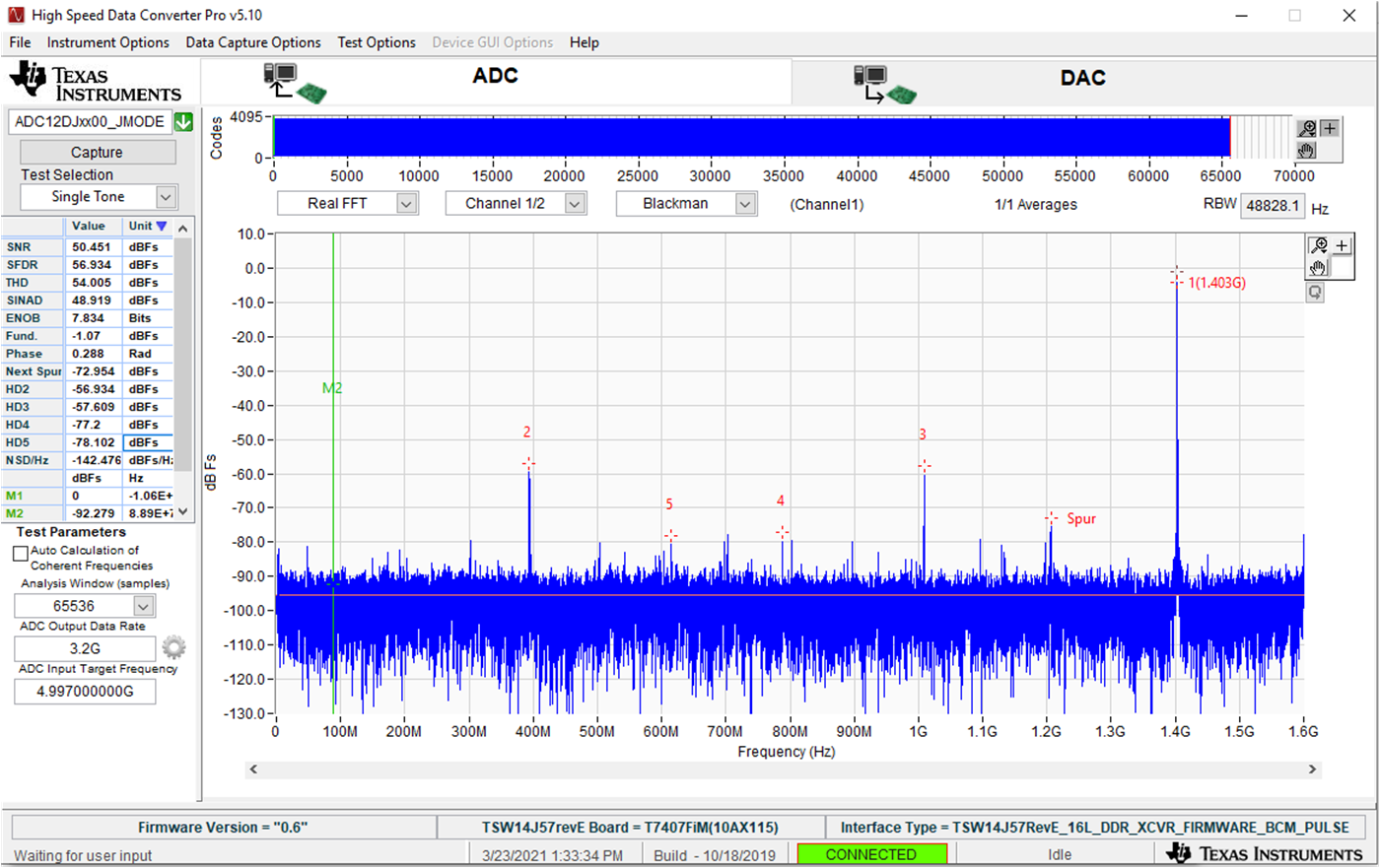

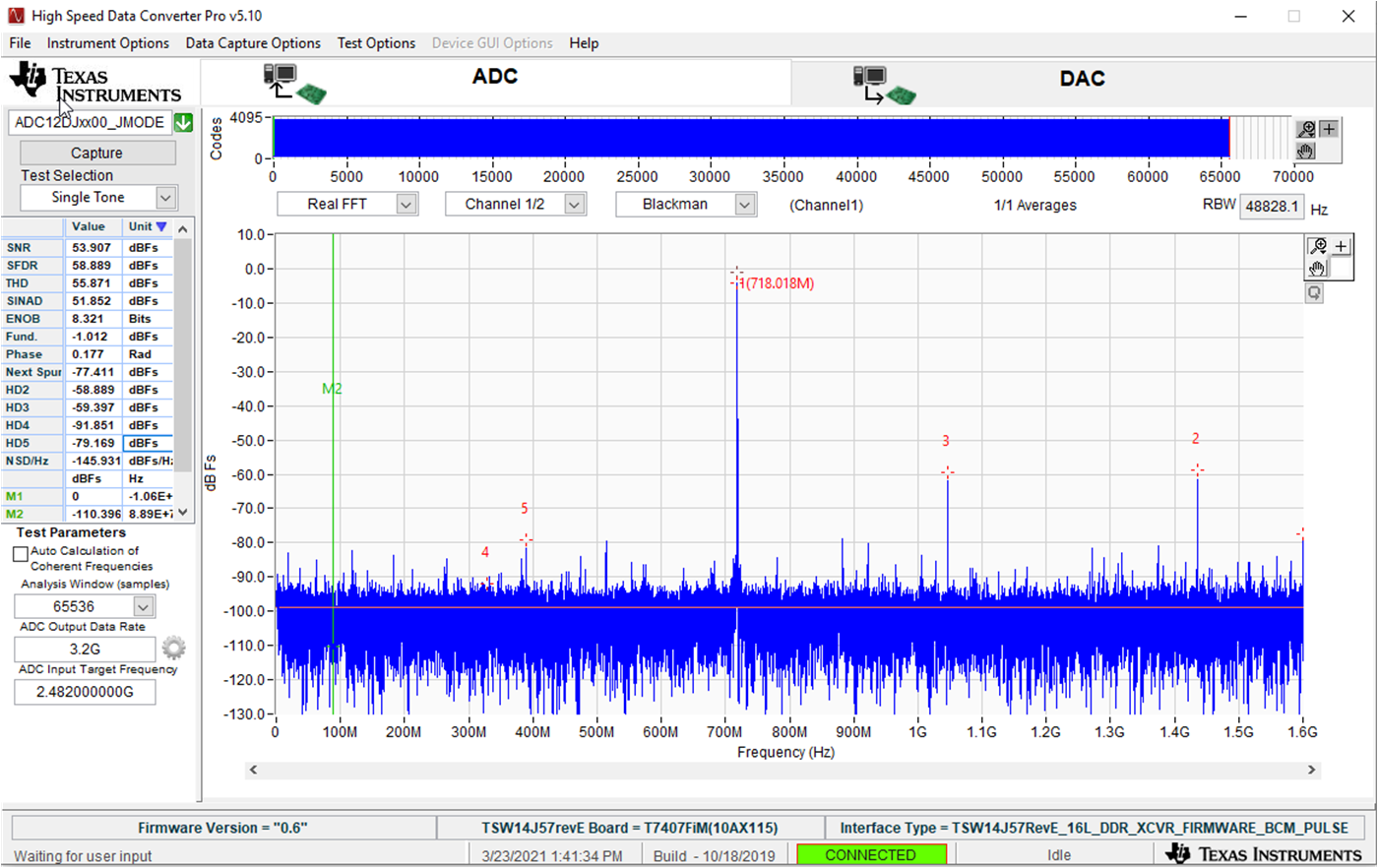

Table 4-2 shows the measured SNR performance of the ADC12DJ3200-SP at various frequencies for –1-dBFS differential inputs and dual channel mode (JMODE3). The comparison between the measured SNR with the ADC12DJ3200EVMCVAL onboard clocks and with TIDA-010191 clocks shows almost similar performance. Figure 4-9 through Figure 4-11 show the spectral results at a 3200-MHz sampling frequency in single-channel mode.

Table 4-2 SNR Measurement

| INPUT FREQ (MHz) | ADC DATA SHEET SNR (dBFS) | ADC12DJ3200EVM ONBOARD CLOCK MEASURED (dBFS) | TIDA-010191 MEASURED (dBFS) |

|---|---|---|---|

| 997 | 55.5 | 55 | 55.6 |

| 2482 | 55 | 53.4 | 53.9 |

| 4997 | 53 | 51.4 | 50.4 |

Figure 4-9 Noise Floor at 99-MHz Carrier

Frequency

Figure 4-9 Noise Floor at 99-MHz Carrier

Frequency Figure 4-11 Noise Floor at 1403-MHz Carrier

Frequency

Figure 4-11 Noise Floor at 1403-MHz Carrier

Frequency Figure 4-10 Noise Floor at 718-MHz Carrier

Frequency

Figure 4-10 Noise Floor at 718-MHz Carrier

Frequency