TIDUF06 August 2022

- Description

- Resources

- Features

- Applications

- 5

- 1System Description

- 2System Overview

- 3Hardware, Testing Requirements, and Test Results

- 4Design Files

- 5Related Documentation

- 6Trademarks

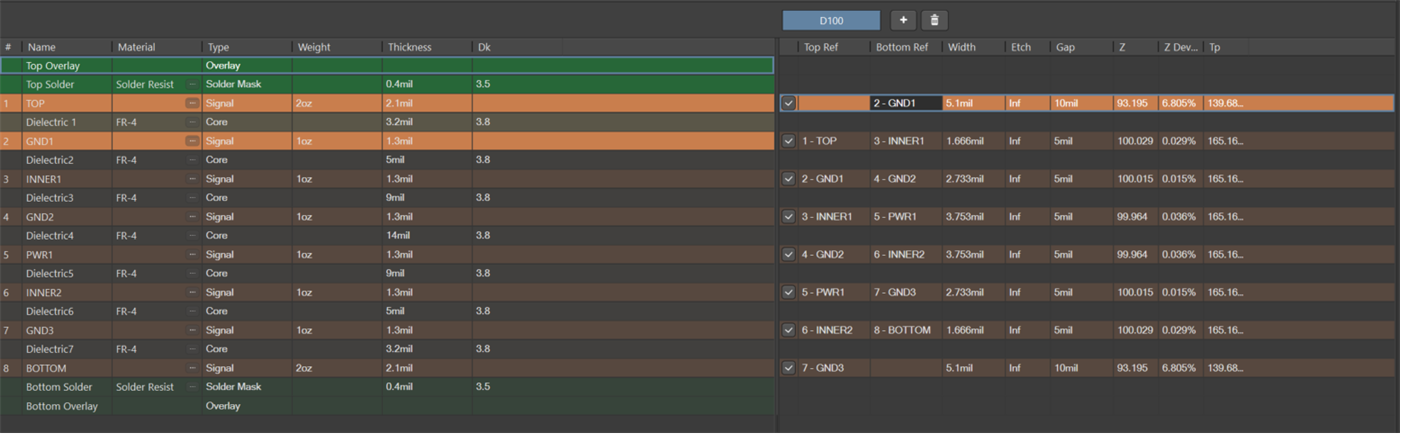

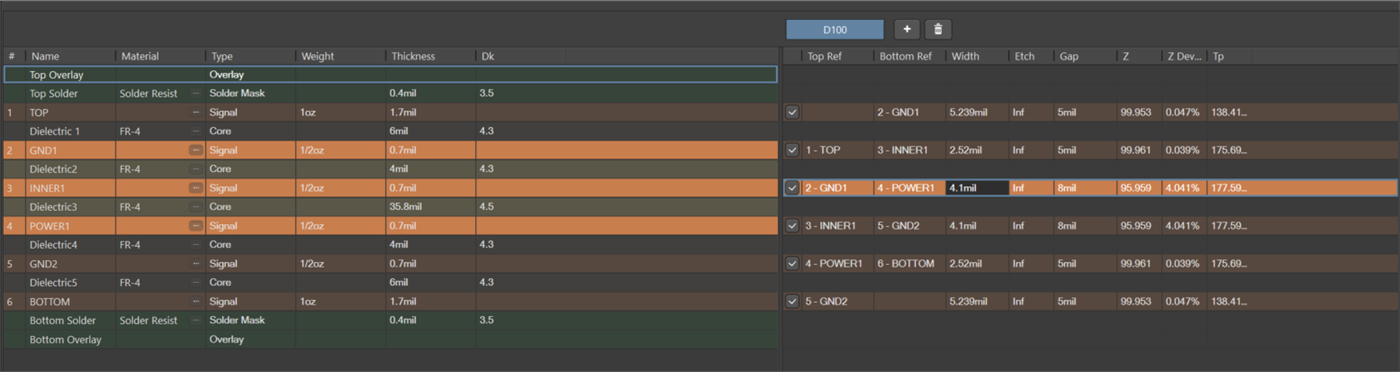

4.3.2 PCB Layer Stackup

Figure 4-2 shows the 8-layer stackup used for the PMIC and serializer board. Two signal layers are required due to the complex routing requirements introduced by I2C, GPIO, clock, and control signals between the PMIC, serializer, and header, which provide an interface with the imager. The separation between planes carrying high-speed CSI data lines should be selected to ensure a characteristic differential impedance of 100 Ω ±10%.

Figure 4-3 shows the 6-layer stackup for the imager board. This has similarly been designed around the target differential impedance of the CSI-2 traces.

Figure 4-2 Eight-Layer Stackup PMIC and

Serializer Board

Figure 4-2 Eight-Layer Stackup PMIC and

Serializer Board Figure 4-3 Six-Layer Stackup Imager

Board

Figure 4-3 Six-Layer Stackup Imager

Board