TIDUF13 November 2022 ADS117L11 , ADS127L11

- Description

- Resources

- Features

- Applications

- 5

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Hardware, Software, Testing, and Test Results

- 5Design and Documentation Support

- 6About the Author

4.1.2.5.3 Parallel SDI Mode and Parallel SDO Mode

In parallel SDI mode and parallel SDO mode, CS and SCLK are shared between all ADCs, and separate parallel SDI, SDO lines are used. This allows independent configuration of the ADCs.

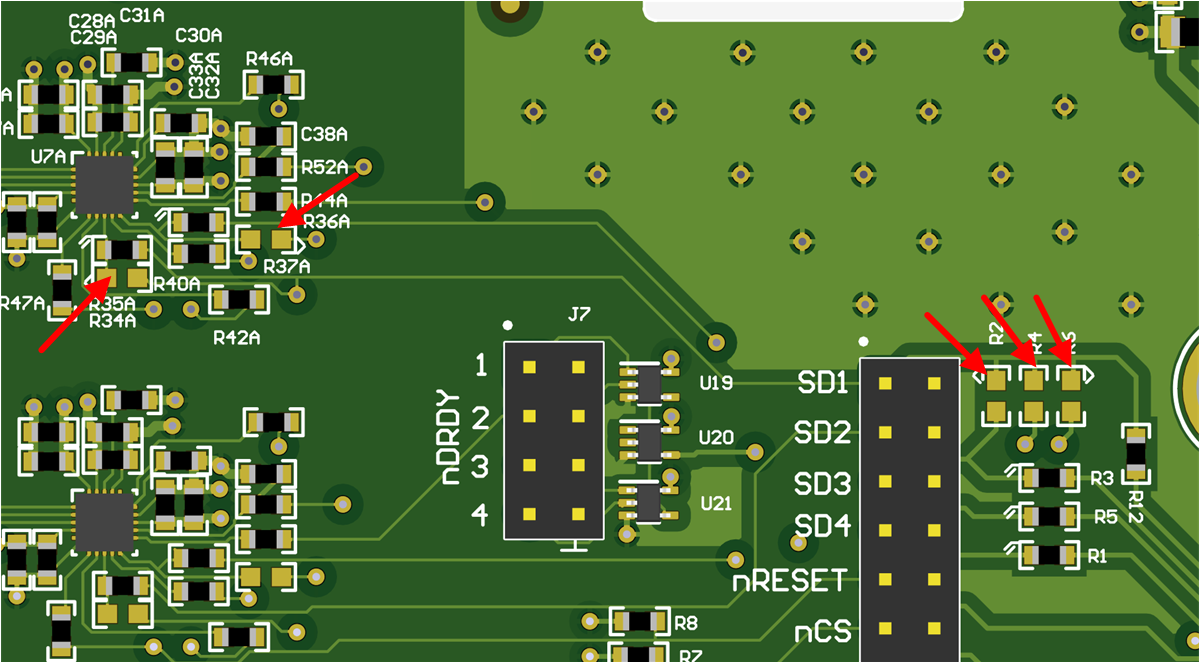

The following board assembly is required to enable the parallel SDI and parallel SDO mode:

- R35x, R37x (all channels), remove R2, R4, R6

Note: Figure 4-5

shows that all resistors with the small triangle

(daisy) are removed, and all resistors with

parallel lines are assembled.

Note: The default assembly has a 16-MHz crystal. Using

this crystal, parallel modes can only achieve a

600-kSPS data rate from the ADCs. To unlock the

full speed of the ADCs, replace the 16 MHz with a

25-MHz crystal.

Figure 4-5 Parallel SDI Variant

Figure 4-5 Parallel SDI Variant