TIDUF13 November 2022 ADS117L11 , ADS127L11

- Description

- Resources

- Features

- Applications

- 5

- 1System Description

- 2System Overview

- 3System Design Theory

- 4Hardware, Software, Testing, and Test Results

- 5Design and Documentation Support

- 6About the Author

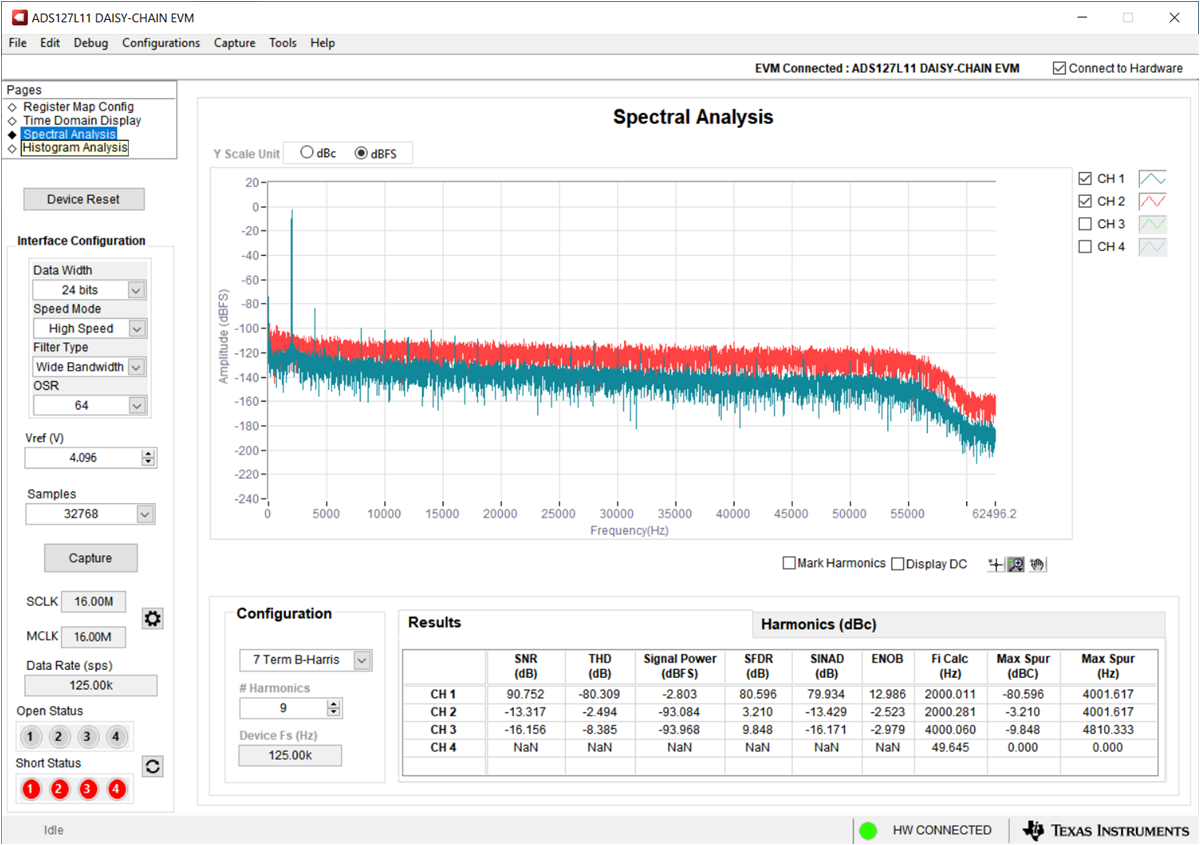

4.4.3 Crosstalk

The 20-VPP, 2-kHz sinusoidal inputs applied to ch1 as in the input range test, ch2 signal power is compared to ch1 signal power. The 20 VPP, 2 kHz is not pure and includes multiple high harmonics.

Figure 4-14 Frequency-Domain Plot of 20-VPP Input at Channel 1

Figure 4-14 Frequency-Domain Plot of 20-VPP Input at Channel 1The ch1 signal level is ch1 is –2.8 dB as expected for full-scale input. While ch2 and ch3 signal levels are at –93 dB. These results indicate a cross-talk level below –90 dB.