TIDUF18A October 2022 – February 2024

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1 CLLLC System Description

- 2 CLLLC System Overview

- 3 Totem Pole PFC System Description

- 4 Highlighted Products

-

5 Hardware, Software, Testing Requirements, and Test Results

- 5.1 Required Hardware and Software

- 5.2

Testing and Results

- 5.2.1 Test Setup (Initial)

- 5.2.2

CLLLC Test Procedure

- 5.2.2.1 Lab 1. Primary to Secondary Power Flow, Open Loop Check PWM Driver

- 5.2.2.2

Lab 2. Primary to Secondary Power Flow, Open Loop CheckPWM

Driver and ADC with Protection, Resistive Load Connected on Secondary

- 5.2.2.2.1 Setting Software Options for Lab 2

- 5.2.2.2.2 Building and Loading the Project and Setting up Debug Environment

- 5.2.2.2.3 Using Real-time Emulation

- 5.2.2.2.4 Running the Code

- 5.2.2.2.5 Measure SFRA Plant for Voltage Loop

- 5.2.2.2.6 Verify Active Synchronous Rectification

- 5.2.2.2.7 Measure SFRA Plant for Current Loop

- 5.2.2.3 Lab 3. Primary to Secondary Power Flow, Closed Voltage Loop Check, With Resistive Load Connected on Secondary

- 5.2.2.4 Lab 4. Primary to Secondary Power Flow, Closed Current Loop Check, With Resistive Load Connected on Secondary

- 5.2.2.5 Lab 5. Primary to Secondary Power Flow, Closed Current Loop Check, With Resistive Load Connected on Secondary in Parallel to a Voltage Source to Emulate a Battery Connection on Secondary Side

- 5.2.3 TTPLPFC Test procedure

- 5.2.4 Test Results

- 6 Design Files

- 7 Software Files

- 8 Related Documentation

- 9 Terminology

- 10About the Author

- 11Revision History

5.2.2.5.5 Measure SFRA for Closed Current Loop in Battery Emulated Mode

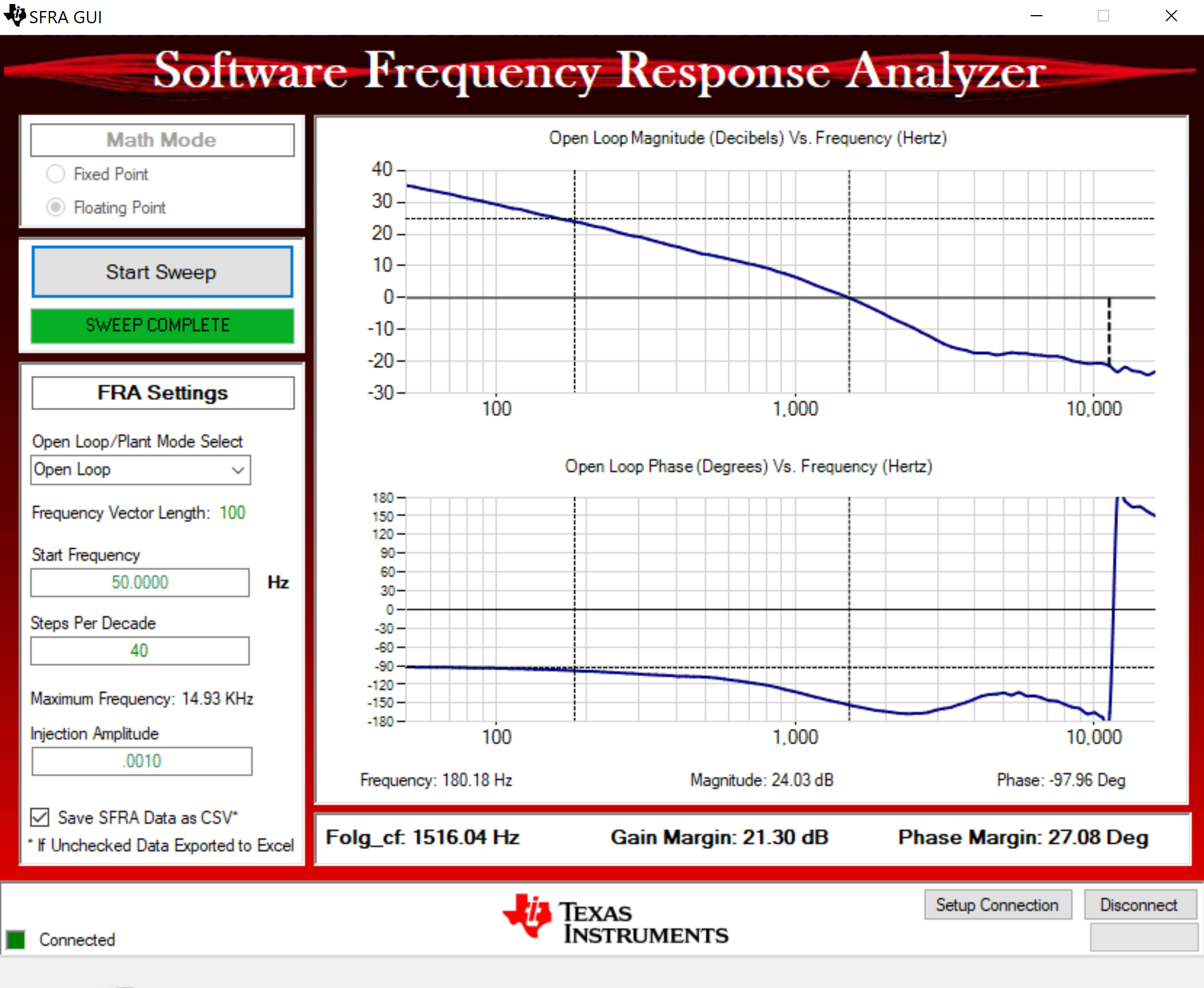

- The SFRA is integrated in the software of this build to verify that the designed compensator provides enough gain and phase margin by measuring on hardware. To run the SFRA, keep the project running, and navigate to <Install directory >\C2000Ware_DigitalPower_SDK_<version>\libraries\sfra\gui\SFRA_GUI.exe. The SFRA GUI will pop up.

- Select the options for the device on the SFRA GUI; for example, for F280039, select floating point. Click on setup connection. In the pop-up window, deselect the boot-on-connect option, select an appropriate COM port, and click OK. Return to the SFRA GUI and click Connect.

- The SFRA GUI will connect to the device. A SFRA sweep can now be started by

clicking Start Sweep. The complete SFRA sweep will take a few minutes to

finish. Activity can be monitored by seeing the progress bar on the SFRA GUI;

and also by checking the flashing of blue LED on the back of the control card,

which indicates UART activity. Once complete, a graph with the open loop plot

will appear, as shown in Figure 5-29.

Figure 5-29 SFRA Open Loop Plot

for the Closed Current Loop With Battery Connection Emulated (Vprim 400

V, Vsec 300 V, Power 1.972 kW, Lab 5)

Figure 5-29 SFRA Open Loop Plot

for the Closed Current Loop With Battery Connection Emulated (Vprim 400

V, Vsec 300 V, Power 1.972 kW, Lab 5)The Frequency Response Data is also saved in the project folder, under an SFRA Data Folder, and is time-stamped with the time of the SFRA run.

Test the SFRA at different current set points, making sure the period is not clamped, to verify that the system is stable across the operable range.

- This verifies the Lab 5current loop design.

- To bring the system to a safe stop, bring the input VPRIM voltage down to zero. Observe the voltages and currents on the watch window go down to zero.

- Fully halting the MCU when in real-time mode is a two-step process. First, halt the processor by using the Halt button on the toolbar

, or by using Target → Halt. Then, take the MCU out of real-time mode by clicking on

, or by using Target → Halt. Then, take the MCU out of real-time mode by clicking on  . Finally, reset the MCU

. Finally, reset the MCU  .

. - Close the CCS debug session by clicking on Terminate Debug Session

(Target → Terminate

all).

(Target → Terminate

all).