TIDUF23 may 2023

- Description

- Resources

- Features

- Applications

- 5

- 1System Description

- 2System Overview

-

3Hardware, Software, Testing Requirements,

and Test Results

- 3.1 Hardware Requirements

- 3.2 Test Setup

- 3.3 Test Procedure

- 3.4 Test Results

- 4General Texas Instruments High Voltage Evaluation (TI HV EVM) User Safety Guidelines

- 5Design and Documentation Support

- 6Terminology

3.4.1 Isolated Bias Supply

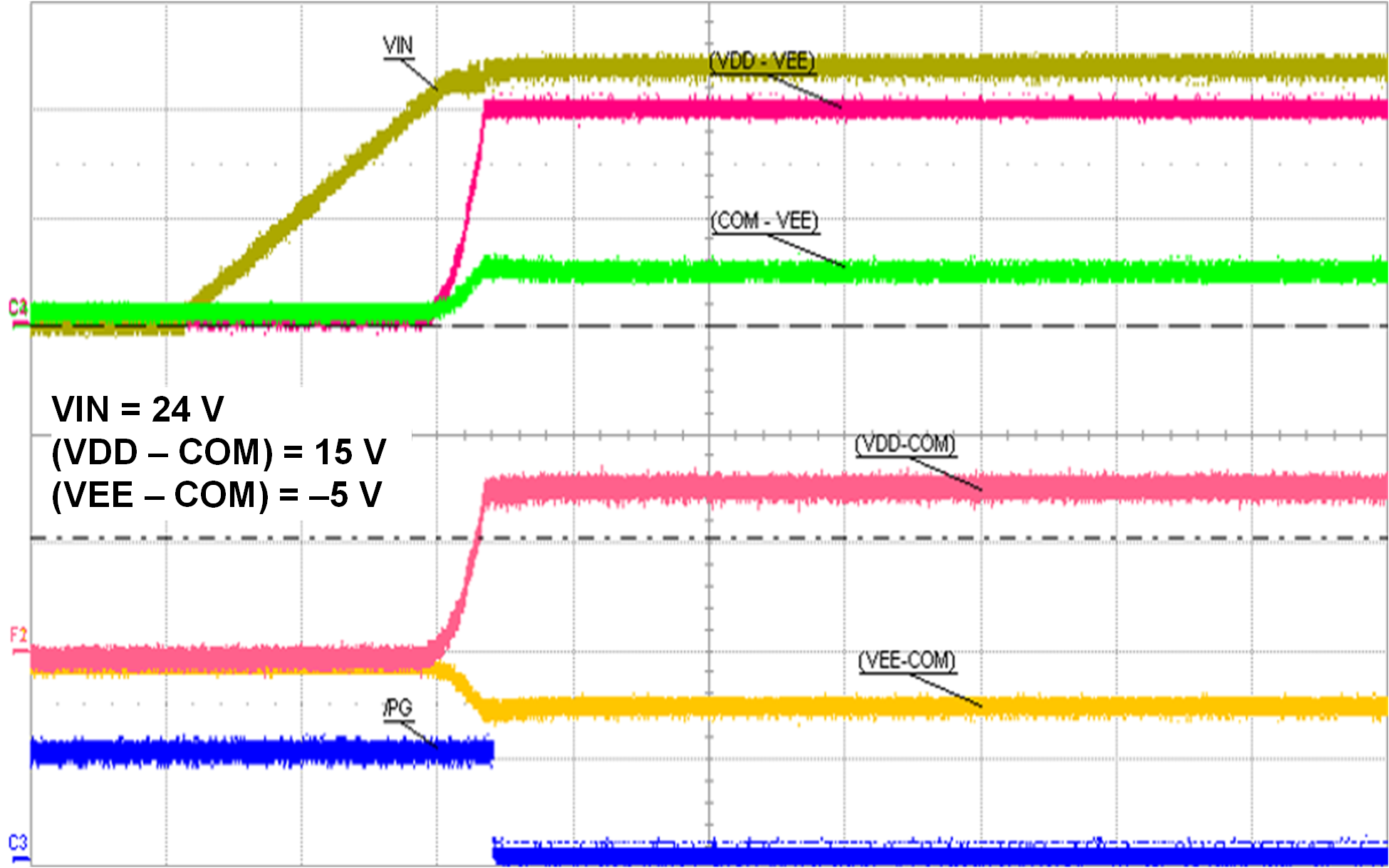

The startup behavior of UCC14240-Q1 is validated as shown in Figure 3-18.

Figure 3-18 UCC14240-Q1 Power-up

Sequence

Figure 3-18 UCC14240-Q1 Power-up

SequenceThe load regulation test is performed to verify the stability of UCC14240-Q1. The electronic load is connected between VEE and VCC, with the load steps from 0 to 80 mA. Measured output voltage is presented in Table 3-5.

Table 3-5 UCC14240-Q1 Load

Regulation

| Load(mA) | Vout(V) | Power(W) |

|---|---|---|

|

10 |

18.853 |

0.188 |

|

20 |

18.848 |

0.377 |

|

30 |

18.84 |

0.565 |

|

40 |

18.834 |

0.753 |

|

50 |

18.83 |

0.941 |

|

60 |

18.828 |

1.13 |

|

69 |

18.825 |

1.3 |

|

80 |

18.819 |

1.505 |

The nominal voltage value is 19 V and the equation for the load regulation is:

Equation 6.