TIDUF33 june 2023

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

-

3Hardware, Software, Testing Requirements,

and Test Results

- 3.1 Hardware Requirements

- 3.2 Software Requirements

- 3.3 Test Setup

- 3.4 Test Procedure

- 3.5 Test Results

- 4Design and Documentation Support

- 5About the Author

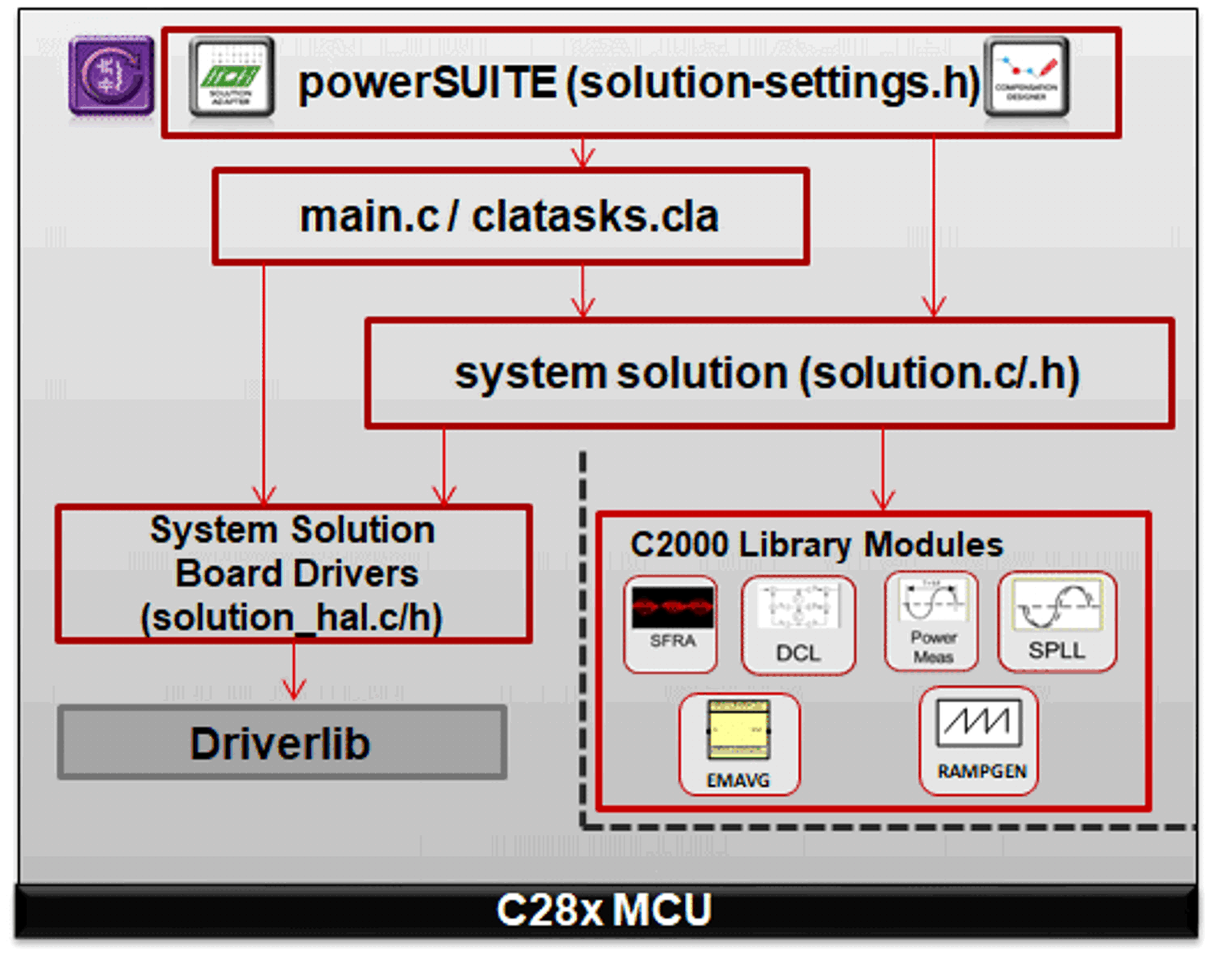

3.2.2 Project Structure

Figure 3-3 Project Structure

Overview

Figure 3-3 Project Structure

OverviewFigure 3-3 shows the general structure of the project. Once the project is imported, the Project Explorer appears inside CCS as shown in Figure 3-4.

Solution-specific and device-independent files that consist of the core algorithmic code are in .c/h.

Board-specific and device-specific files are in _hal.c/h. This file consists of device-specific drivers to run the solution. If the user wants to use a different modulation scheme or a different device, the user is required only to make changes to these files, besides changing the device support files in the project.

The -main.c file consists of the main framework of the project. This file consists of calls to the board and solution file that help in creating the system framework, along with the interrupt service routines (ISRs) and slow background tasks.

For this design, the solution is bt2ph.

The powerSUITE page can be opened by clicking on

the main.syscfg file, listed under the Project Explorer. The powerSUITE page

generates the _settings.h file. This file is the only C language based file

used in the compile of the project that is generated by the powerSUITE page. The

user must not modify this file manually, because the changes are overwritten by

powerSUITE each time the project is saved. _user_settings.h is included by

the _settings.h and can be used to keep any settings that are outside the

scope of powerSUITE tools such as #defines for ADC mapping, GPIOs,

and so forth.

The _cal.h file consists of gain and offset values for current and voltage measurements.

The Kit.json and solution.js files are used internally by powerSUITE, and must not be modified by the user. Any changes to these files results in the project not functioning properly.

The solution name is also used as the module name for all the variables and defines used in the solution. Hence, all variables and function calls are prepended by the BT2PH name (for example, BT2PH_userParam_V_I_ch1). This naming convention lets the user combine different solutions while avoiding naming conflicts.

Figure 3-4 Project Explorer View of the

BT2PH Project

Figure 3-4 Project Explorer View of the

BT2PH ProjectThe BT2PH project consists of three ISRs (ISR3, ISR4, and ISR7). ISR1, ISR2, ISR5, and ISR6 are reserved for future use.

ISR3 is used to sense the input voltage and capacitor voltage of the buck converters. ISR3 is triggered by ADCC conversion complete. ADCC is used to sense input voltage and output voltage of the converter to implement soft-start of the DC/DC.

ISR4 is triggered by the DRDY (Data Ready) Signal of the ADS131M08. The external ADC is programmed for a 15.625-kHz sample rate, which sets the ISR frequency. The ISR runs the current and voltage control loop functions.

ISR7 is triggered by SPI receive FIFO interrupt. The ISR is used to read the external ADC data from FIFO registers.

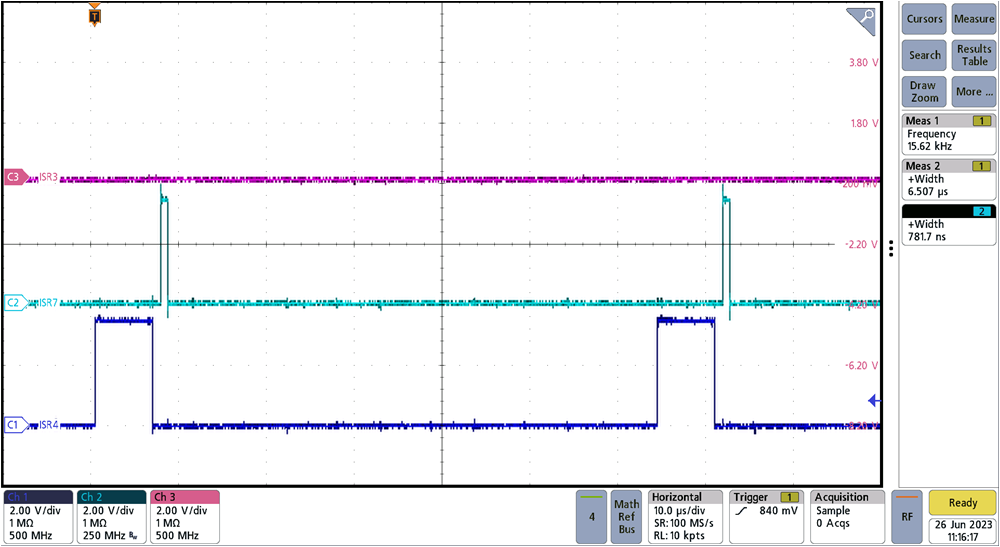

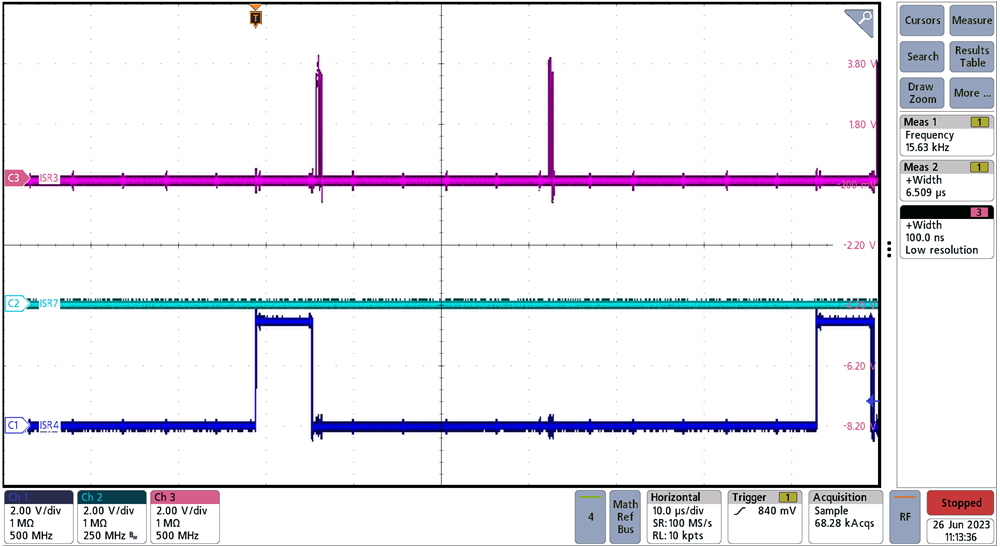

Figure 3-5 and Figure 3-6 show the time taken by ISR3, ISR4, and ISR7. The total time taken three ISRs is less than 8 µs. The ISRs take 12.5% of CPU resources for 15.625-kHz ISR frequency.

Figure 3-5 ISR4 and ISR7 Execution Time

Measurement

Figure 3-5 ISR4 and ISR7 Execution Time

Measurement Figure 3-6 ISR4 and ISR3 Execution Time

Measurement

Figure 3-6 ISR4 and ISR3 Execution Time

Measurement