TIDUF33 june 2023

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

-

3Hardware, Software, Testing Requirements,

and Test Results

- 3.1 Hardware Requirements

- 3.2 Software Requirements

- 3.3 Test Setup

- 3.4 Test Procedure

- 3.5 Test Results

- 4Design and Documentation Support

- 5About the Author

3.4.3.3 Running the Code

- To run this lab, make sure the hardware is set up as outlined in the previous section,Section 3.4.2.

- Run the project by clicking

from the menu bar.

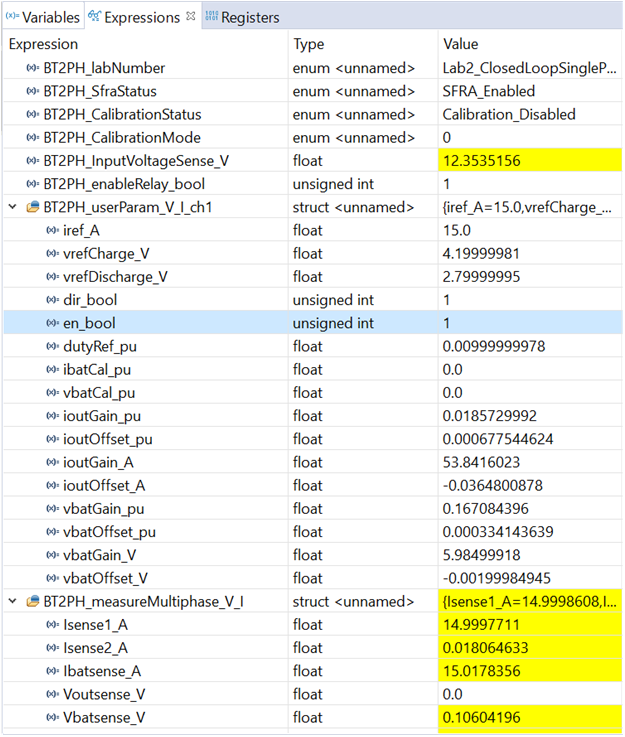

from the menu bar. - In the watch view, check if the BT2PH_InputVoltageSense_V is between 12 V –15 V in the Expression Window.

- Set the following parameters from the

Expression Window:

- Set the BT2PH_enableRelay_bool to 1 to enable the output relay.

- BT2PH_userParam_V_I_ch1->iref_A = 15.0.

- Set the BT2PH_userParam_V_I_ch1->en_bool = 1.

- See Figure 3-25 for the Expression Window settings.

- BT2PH_measureMultiphase_V_I variable shows output current and voltage of the DC/DC converter. Isense1_A display value is close to iref_A setting with ±1 mA error.

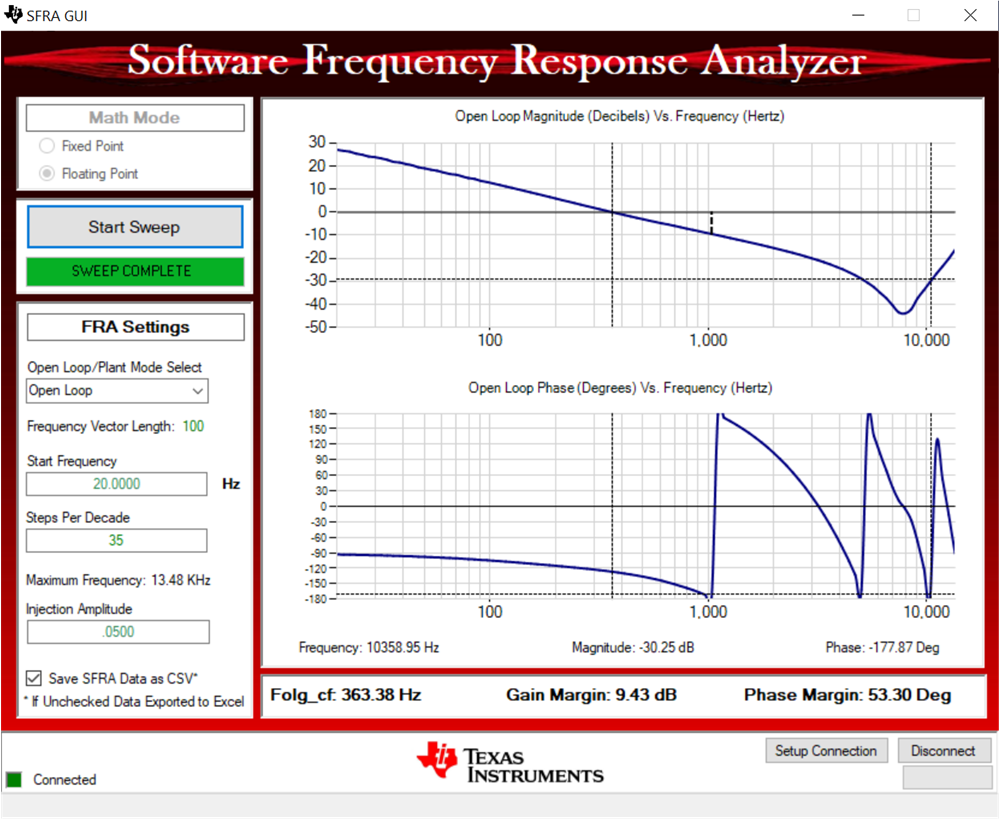

- Figure 3-26 shows the SFRA setup to test the loop stability. Click on Run SFRA icon from the SYSCONFIG page. The SFRA GUI pops up.

- Select the options for the device on the SFRA GUI; for example, for F280039, select floating point. Click on setup connection. In the pop-up window, uncheck the boot-on-connect option and select an appropriate COM port. Click Ok. Return to the SFRA GUI and click the Connect button.

- The SFRA GUI connects to the device. A SFRA sweep can now be started by clicking Start Sweep. The complete SFRA sweep takes a few minutes to finish. Once complete, a graph with the measurement appears, as shown in Figure 3-19.

- The Frequency Response Data is saved in the project folder, under an SFRA Data Folder, and is time-stamped with the time of the SFRA run.

Figure 3-17 Lab 2 Expression Window,

Closed Loop

Figure 3-17 Lab 2 Expression Window,

Closed Loop Figure 3-18 SFRA Setup for Closed-Loop

Current Control

Figure 3-18 SFRA Setup for Closed-Loop

Current Control Figure 3-19 Current Control Closed-Loop

Frequency Response

Figure 3-19 Current Control Closed-Loop

Frequency Response