TIDUF41A October 2023 – June 2024

3.3.2 TCD_PHYL_INTF_UARTTRANSDELAY

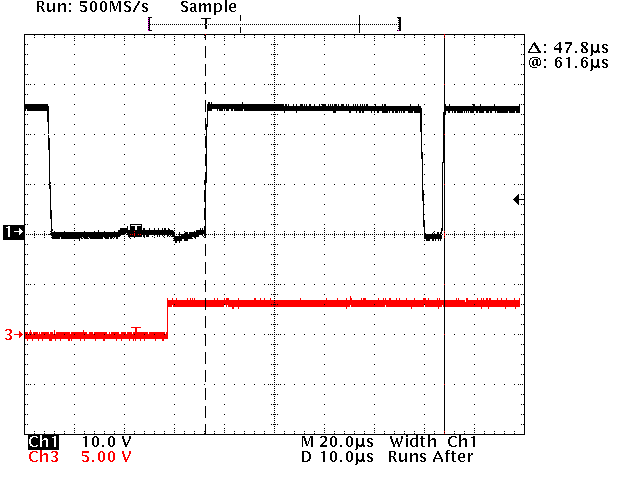

To determine t2 time, the rising edges of the UART frames on the CQ line are observed to measure the time from one frame to the next. The time of the transmission of eleven bits is then subtracted so that only the time between two frames remain. The time is allowed to be between 0 and 3 times the bit time. In case of COM3, a maximum of 13µs is allowed.

Black = C/Q Line, Red = TIOL112

enable signal

Figure 3-19 T2 Measurement,

First Device Response Start Bit to Second Start Bit TransitionEquation 1. 47.8µs – 11 × 4.34µs = 0.06µs, this

equals 0.01 TBIT

A very low t2 time is expected, because the UART transmit buffer is reloaded automatically through direct memory access (DMA). The measurement is limited by the time resolution of the measurement.