TIDUF41A October 2023 – June 2024

3.3.3 TCD_PHYL_INTF_RESPONSETIME

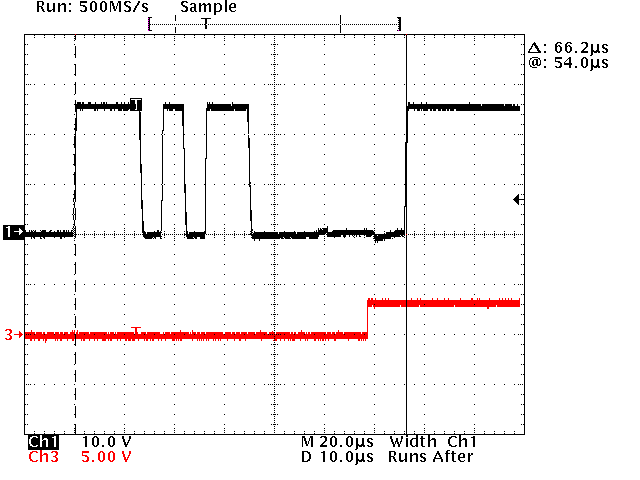

To measure tA, the time between the start bit of the last master message and the start bit of the response from the device is measured. The time of the last message from the master is subtracted. The time is allowed to be between 1 and 10 times the bit time. For COM3 this allows 4.34µs and 43.4µs.

Black = C/Q Line, Red = TIOL112

enable signal

Figure 3-20 TA Measurement, Master Start

Bit Transition to Device Start Bit TransitionEquation 2. 66.2µs – 11 × 4.34µs = 18.46µs, this equals 4.25

TBIT

The measured time is within the limits.