TIDUF71 March 2024

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

- 3Hardware, Software, Testing Requirements, and Test Results

- 4Design and Documentation Support

- 5About the Author

3.7.1.1 The Easy Way - Internal PLL/VCO

There is an option to use the internal PLL/VCO of the AFE7950-SP device. The “easy way” uses the existing connections and only modifies the software programming. The technique is to program the LMX2694 to supply a 491.52MHz reference signal instead of the high frequency clock. Though this is the easy modification on the reference board, in practice, the appropriate approach as outlined in the next section is to use only the LMK04832-SEP to generate the clock reference to the AFE7950-SP.

This approach follows the primary bring up procedure, but substitutes a different LMX2694 file and a different Latte file.

- LMX2694-SEP: LMX2694-SEP_122p88Ref_122p88PFD_491p52M.tcs

- Latte: AFE7950-SP_EVM_Mode2H.py

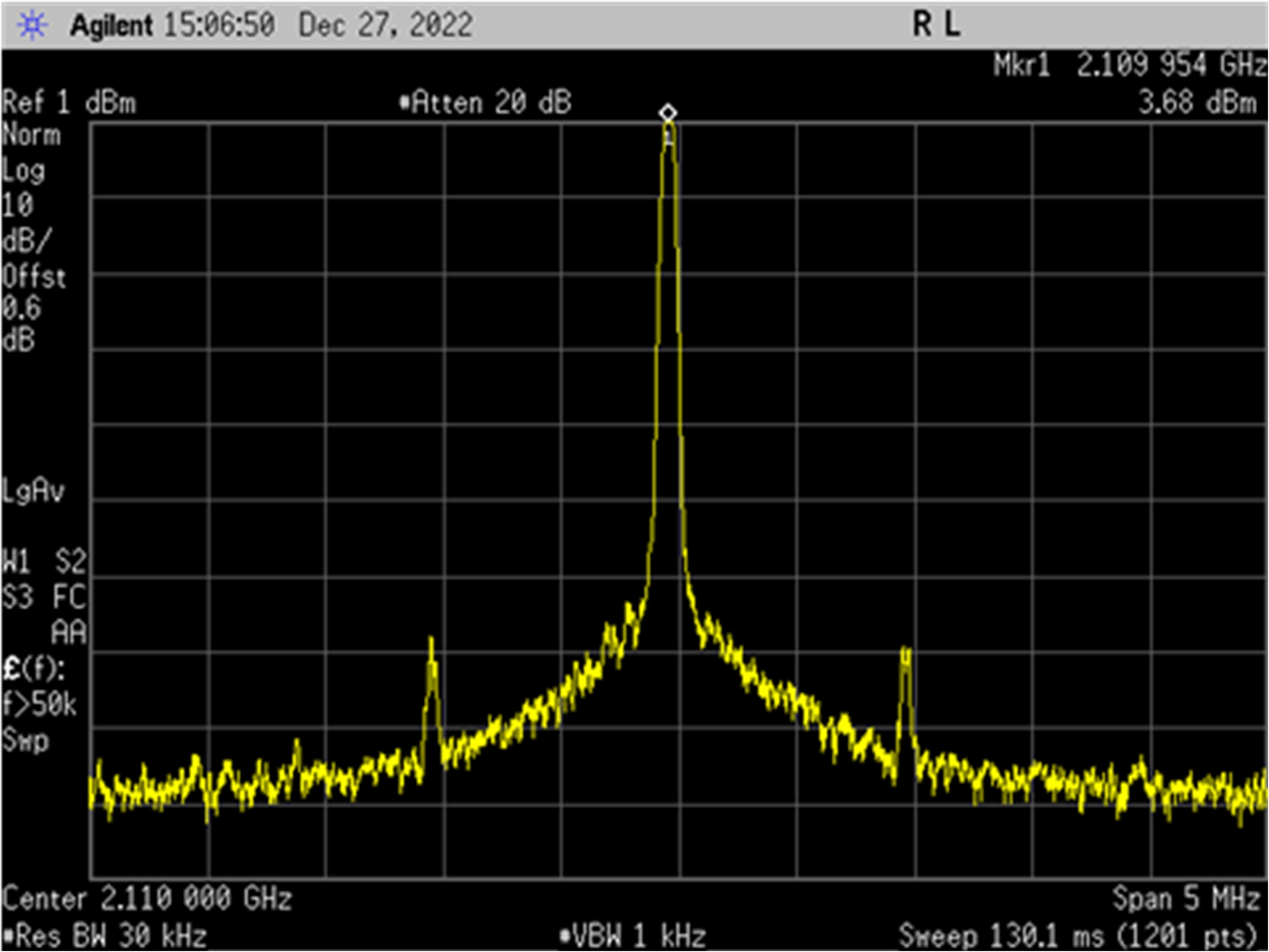

This LMX file outputs a 491.52MHz signal that the AFE7950-SP uses as the reference for the internal PLL/VCO. The Latte file engages the internal PLL/VCO. As an example, Figure 3-8 shows the TXA output spectrum when using the internal PLL/VCO.

Figure 3-8 TXA Output Spectrum with

AFE7950-SP Internal PLL/VCO

Figure 3-8 TXA Output Spectrum with

AFE7950-SP Internal PLL/VCO