TIDUF71 March 2024

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

- 3Hardware, Software, Testing Requirements, and Test Results

- 4Design and Documentation Support

- 5About the Author

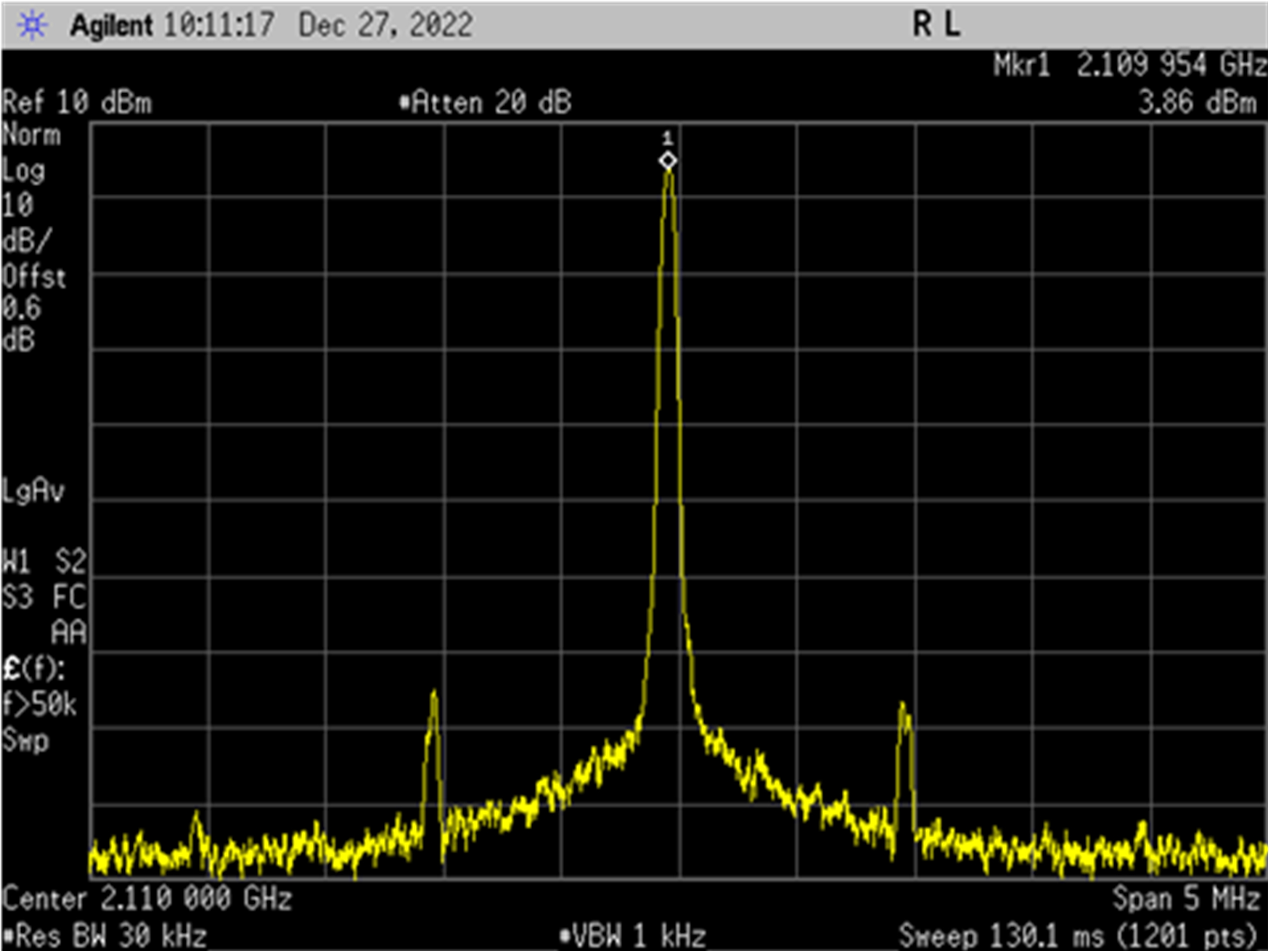

3.6.1 TXA/B DAC Output Test Results

The config file is setup on channels TXA and TXB with the NCO set to 2.1GHz. The TSW14J56 is setup with a tone at 10MHz offset. Expect the output tone at about 2110MHz. Note, the offset is not exactly 10MHz due to the multi-tone set-up. Figure 3-3 shows the output tone performance.

The spur at 1MHz offset is from the 1.2V, 1.8V, and 3.3V DC-DC switchers. The 1.2V supply couples most prominently to the external clock due to the proximity.

The output power is approximately 4dBm. Note, the config file engages a 10dB attenuator on the AFE7950-SP to maintain that the TRF0208 device is not over-driven.

Figure 3-3 TXA/B DAC Output

Performance

Figure 3-3 TXA/B DAC Output

Performance