TIDUF71A March 2024 – November 2024

- 1

- Description

- Resources

- Features

- Applications

- 6

- 1System Description

- 2System Overview

- 3Hardware, Software, Testing Requirements, and Test Results

- 4Design and Documentation Support

- 5About the Author

- 6Revision History

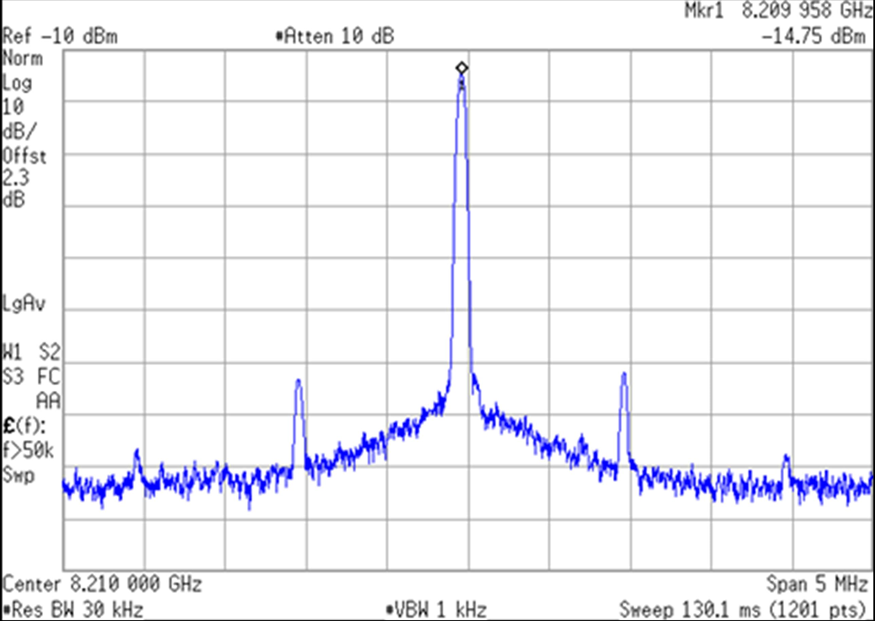

3.6.2 TXC/D DAC Output Test Results

The config file is setup on channels TXC and TXD with the NCO set to 8.2GHz. The expected output tone is about 8210MHz. These channels do not use the TRF0208-SEP; instead there is a passive balun. Hence, there is no need to engage the digital attenuators. Figure 3-4 shows the output performance.

As before, the 1.0MHz offset spurs are from the DC-DC converters. TXD is well matched for 8.2GHz; however, TXC has the balun on the opposite side of the board and the additional via inductance skewed the match from optimum. As such, this channel has low gain which can be recovered with a layout or match tweak.

Figure 3-4 TXD DAC Output

Performance

Figure 3-4 TXD DAC Output

Performance